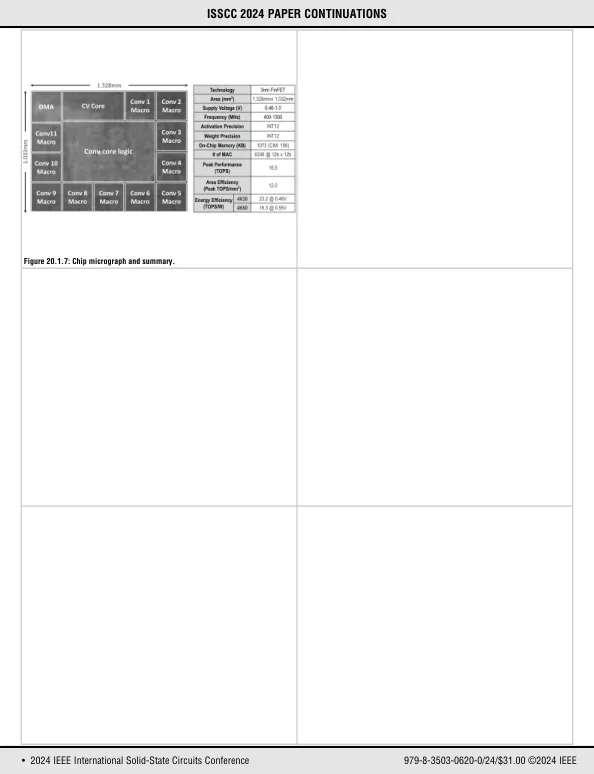

3 TSMC,Hsinchu,Taiwan *同样信誉的作者(ECAS)增强视频质量对于在包括手机,电视和监视器在内的智能设备上获得了增强的用户体验至关重要。实用的硬件设计应在与带宽,区域和能源预算相关的严格限制下提供最小资源的高性能。在图像处理任务中,深入学习算法的广泛用法(包括超分辨率(SR)和降噪(NR))进一步强调了能量效率硬件解决方案的必要性。因此,新兴的关键要求是在实时和高分辨率方案中部署这些算法。但是,实现这一目标提出了几个挑战,如图20.1.1:1)高分辨率网络推断大大增加了由于其计算复杂性,低稀疏性和高精度要求而引起的功耗; 2)频繁的高精度数据交易到外部内存会导致与带宽使用相关的大量功率使用; 3)有效和灵活的机制对于支持各种网络结构和操作至关重要。域特异性加速器提供了一种有希望的解决方案来处理计算需求。总的来说,这些创新使NVE能够在0.46V时达到23.2吨/w的端到端能量效率,而面积的效率为12.0吨/mm 2的面积为1.0V。图20.1.2显示了整体体系结构,包括卷积(Conv)核心,计算机视觉(CV)核心和直接内存访问(DMA)模块。图20.1.3概述了DCIM核心设计和工作流。在这项工作中,提出了在3NM技术中制造的12B位数基于CIM的神经视觉增强引擎(NVE),其特征是:1)无重量的无重量数字计算机(DCIM)发动机,其重量切换率降低,以增强计算能力的功能; 2)卷积元素(CE)融合建立了工作负载平衡的管道架构,从而减少了外部内存访问和功耗; 3)自适应数据控制和带状优化机制支持DCIM中的卷积和转置卷积,并改善了利用率,并且对有效的数据遍历进行了优化的执行流。Conv Core包含11个阶段的管道CE,用于存储中间数据的功能映射存储器,CE融合接口和融合控制。a fine编译器分区将计算图分隔为时区域的循环和太空划分的条纹,以优化吞吐量和内存访问,然后在命令描述符中编码重量和设置。DMA将描述符解码并从DRAM或TCM中加载输入特征映射,以基于线的栅格扫描顺序为核心。在管道流中,每个CE从特征映射存储器和前面的管道阶段收集数据,并将其分配到DCIM宏。宏计算每个周期中的8组点产量,其中每组涉及72对12B元素。权重局部存储在18组行中,其特定集由行选择器选择。在实验结果中证明了使用更频繁使用的8b的12B激活和权重的必要性。在拟议的行开关更高的精度有助于产生更平滑的边缘和最小化超分辨率任务中的噪声。同样,在降低降噪任务中,更高的精度会导致较少的流动性,并产生更重的图像。DCIM的高效率很大程度上是由于记忆和逻辑之间的数据移动降低,这对于最大程度地减少了频繁的重量重音至关重要。先前的工作[1]引入了带有乒乓重量更新的2行DCIM设计,但除了dcim宏中的乒乓球重量存储外,它会引起重量重加载和其他SRAM的电源和面积。利用像素级网络中的权重较少,采用了18行DCIM来存储所有权重并消除重新加载。与[1]中提出的方法相比,这种方法分别将面积和功率降低了31%和28%。影响DCIM效率的另一个因素是重量排开关的频率,这是计算不同权重集合时发生的能量耗尽操作。延长行开关周期可以减少能源消耗,但它还需要在输入和输出缓冲区中存储更多像素,从而导致较大的面积在开销中。

ESSCC 2024-机器学习加速器

主要关键词