机构名称:

¥ 1.0

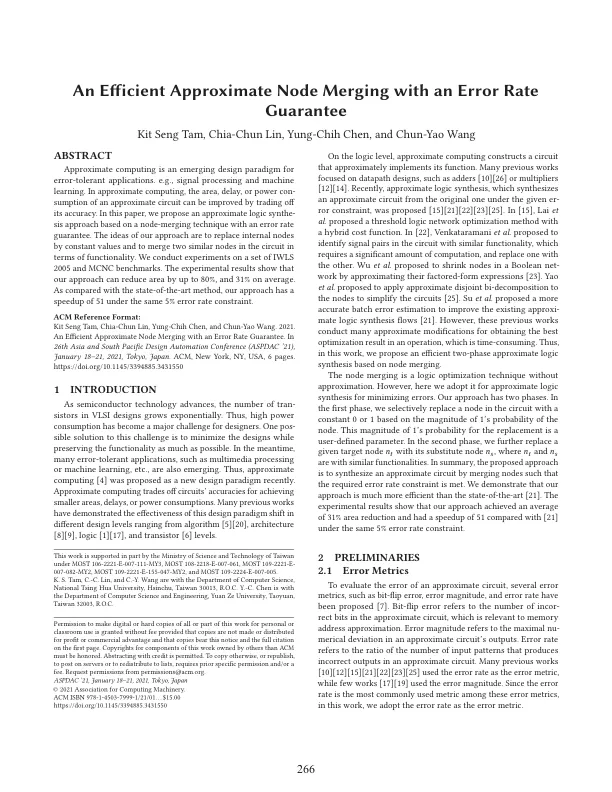

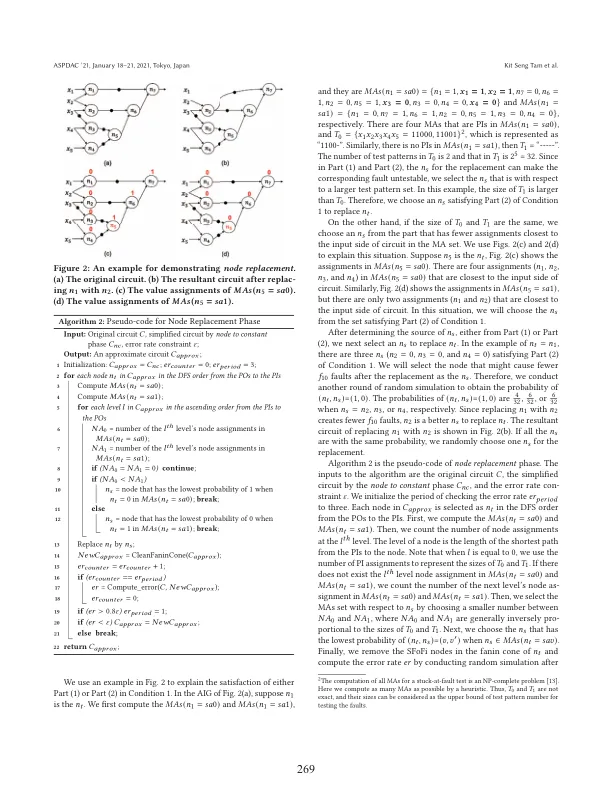

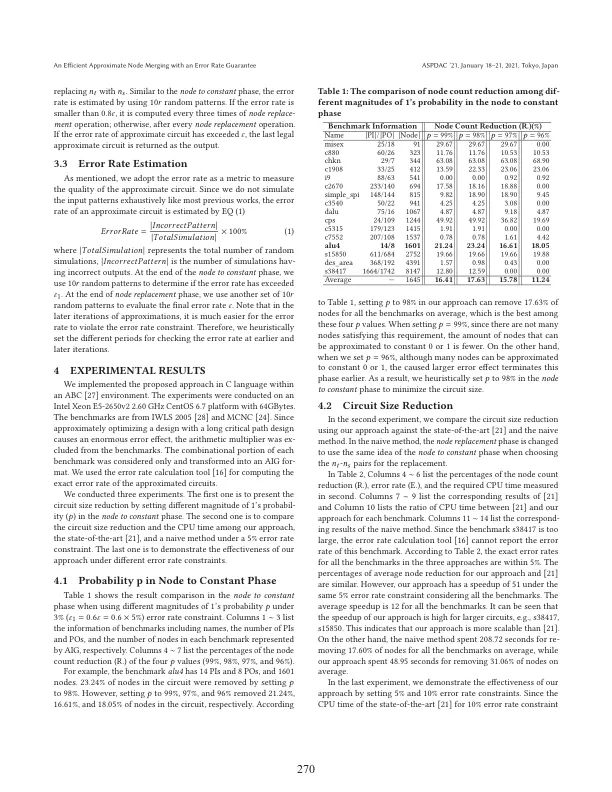

近似计算是针对容错应用的一种新兴设计范式,例如信号处理和机器学习。在近似计算中,近似电路的面积、延迟或功耗可以通过牺牲其精度来改善。在本文中,我们提出了一种基于节点合并技术并保证错误率的近似逻辑综合方法。我们的方法的思想是用常数值替换内部节点,并合并电路中两个功能相似的节点。我们在一组 IWLS 2005 和 MCNC 基准上进行了实验。实验结果表明,我们的方法最多可以减少面积 80%,平均减少 31%。与最新方法相比,在同样 5% 的错误率约束下,我们的方法加速了 51 倍。

一种具有错误率保证的高效近似节点合并方法