机构名称:

¥ 1.0

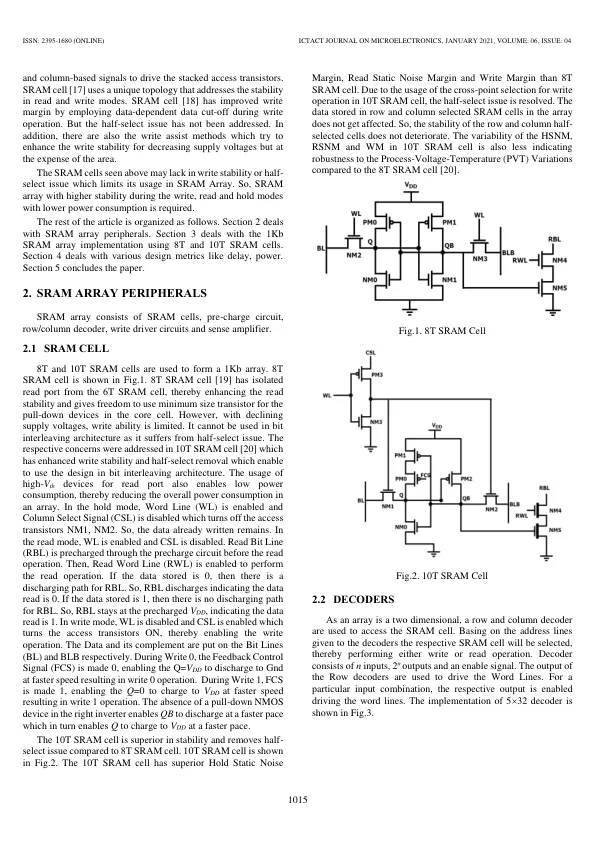

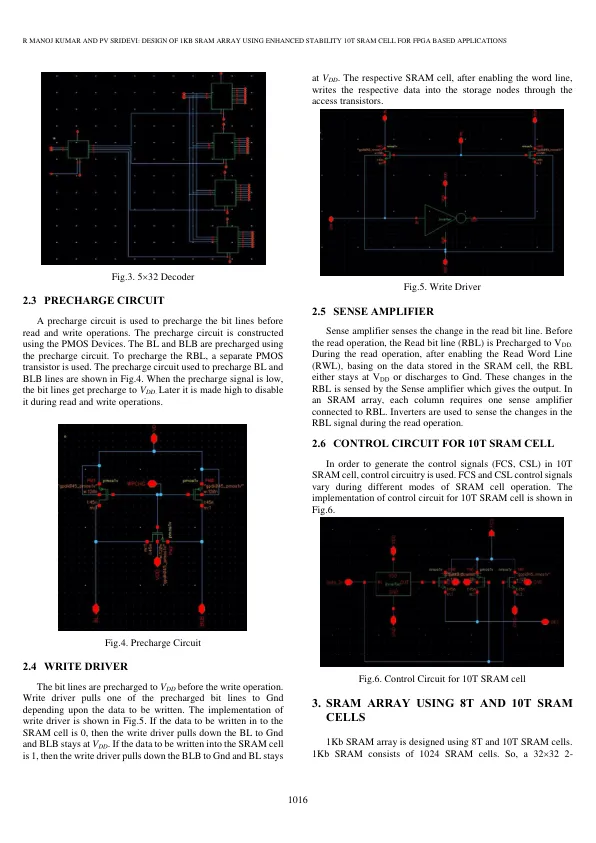

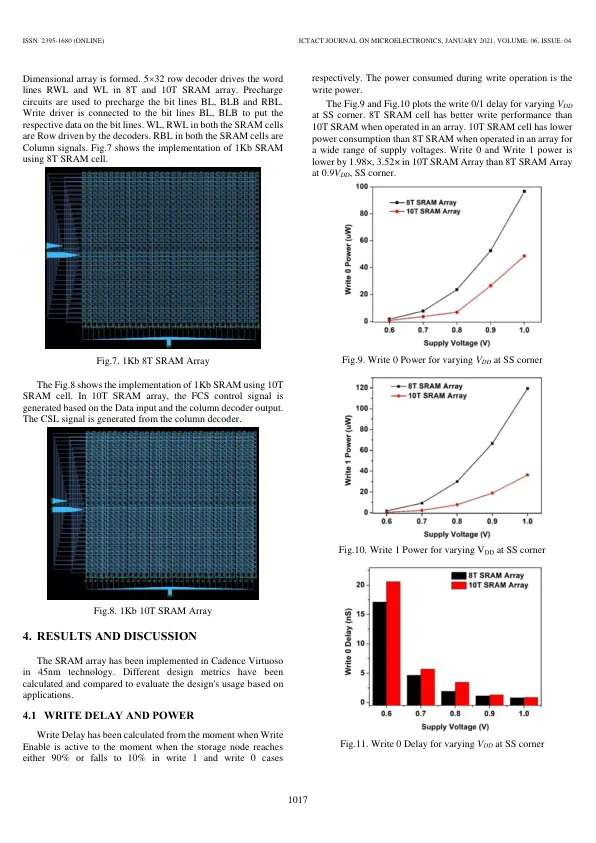

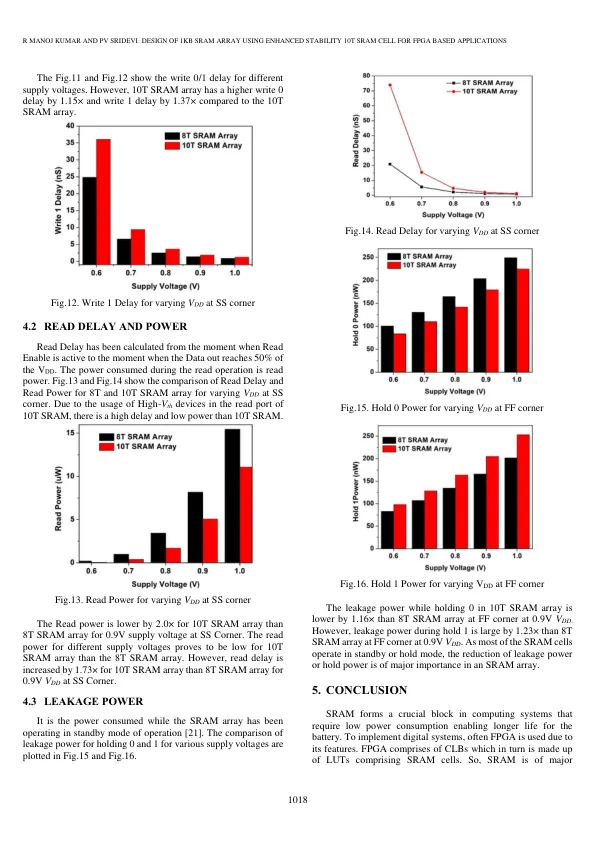

用于FPGA的摘要SRAM需要更高的稳定性和低功耗。8T SRAM单元随着供应电压的降低而降低了写入稳定性。10T SRAM单元具有较高的写入稳定性,因为其中一个逆变器中的上拉路径中使用了截止开关。具有低功耗和较高稳定性的SRAM阵列的设计至关重要。so,已经设计并比较了使用8T和10T SRAM细胞的1KB SRAM阵列进行不同的设计指标。写0和写1功率较低1.98×,10t sram阵列中的3.52××SRAM阵列在0.9V DD,SS角下方。由于在10T SRAM单元中使用高V th晶体管,读取功率在SS角的0.9V V dd较低1.6倍。保持0时的泄漏功率在10T SRAM阵列中低于1.13×,比在0.9V V dd处的FF拐角处的8T SRAM阵列中的泄漏功率。对设计指标进行了广泛的电源电压评估。设计在45nm技术节点中以Cadence Virtuoso实现。

使用增强稳定性10T SRAM单元格的1KB SRAM阵列设计

主要关键词