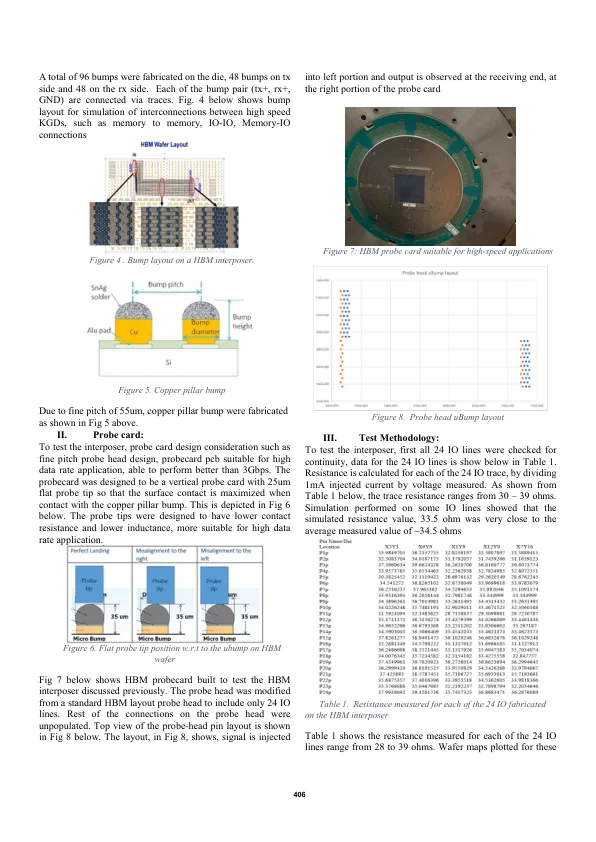

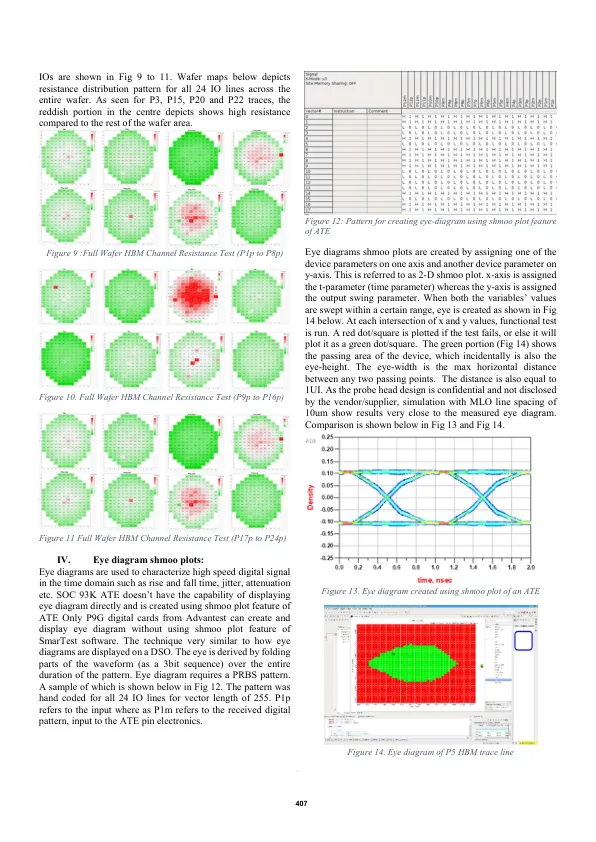

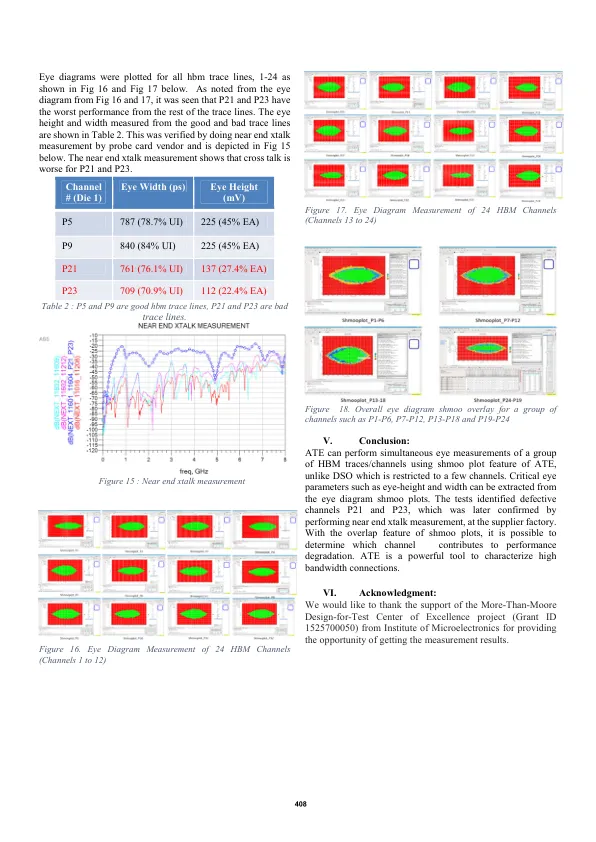

使用自动测试设备 (ATE)、SOC 93K 并行测试多个高速通道 Ratan Bhimrao Umralkar、Li Kangrong。新加坡 A*STAR 微电子研究所 2 Fusionopolis Way, #11 Innovis Tower,新加坡 138634 ratan_bhimrao_umralkar@ime.a-star.edu.sg,li_kangrong@ime.a-star.edu.sg,摘要高带宽存储器 (HBM) 需要在安装在中介层上的 IO 芯片和 IO 到存储器堆栈之间进行高速数据传输。来自不同供应商的 KGD HBM 堆栈和 IO 芯片安装在高数据速率/带宽中介层上。在多芯片设备封装过程中,将测试从最终测试转移到晶圆级需要高昂的设备成本[4],例如探测器、探测卡,但废品成本较低。就目前的封装技术(如 2.5D/3D 和 Chiplets)而言,较低的废料成本意味着更高的产量。一旦将 KGD 安装在中介层(和基板)上,如果中介层经测试有故障,则无法将其移除,从而浪费整个封装 [4]。本文讨论了在安装 KGD HBM、IO 芯片和其他芯片之前测试中介层上高速数据速率互连的测试方法(见下图 1)。高端 DSO(数字存储示波器)可以相对轻松地测试 1 到 4 个通道。但是,当通道数为 8、16 位总线等组时,使用 ATE 会变得更有优势。其中一个主要优势是,ATE 可以同时测试多个通道,因此使用 ATE 测试多个通道变得更加可行。不同通道的结果可以叠加在单个图上。最终的叠加图提供了有关哪个通道输出影响高速总线整体性能的重要信息。眼图 [2] 是一种重要的信号完整性测试,可用于了解数字系统中通信信道的质量,眼图提供有关传输线质量和信道带宽的信息。本文讨论了如何有效地使用 ATE 来构建眼图,使用 ATE 的 shmoo 图功能,恰当地称为眼图 shmoo 图。此外,由于 ATE 可以同时测试多个通道,因此可以加快大规模测试速度,例如测试整个晶圆。此处开发的测试方法是细间距高速通道项目的一部分,其中使用 24 个高速通道构建晶圆测试,以模拟具有 55um 凸块间距的 HBM(高带宽存储器)应用,以展示使用 ATE 的细间距 [3] 探测和功能。对于同时测试的 24 个通道,结果显示 2 条迹线的眼宽和眼高小于其余迹线,但本文的重点不是这些结果,而是如何在 ATE 级别测试中实现眼图。当前设置使用 Advantest 93K 测试仪和 12 英寸 Tel 探测器。ATE 包含 3 个 PS1600 卡,最大数据速率为 1.6Gbps。对于高达 9G 的更高数据速率,可以使用 PS9G 卡。使用 PS1600 卡,我们能够测试高达 1Gbps 的速度,并为所有 24 条迹线绘制眼图。构建了一个细间距、55um 的探针卡,具有 24 个 HBW 通道,用于测试 HBM 晶圆并验证测试方法。下图 1 显示了使用 shmoo 图为其中一个通道 P9 绘制的眼图。基本参数如

1 使用自动化测试多个高速通道...

主要关键词