机构名称:

¥ 1.0

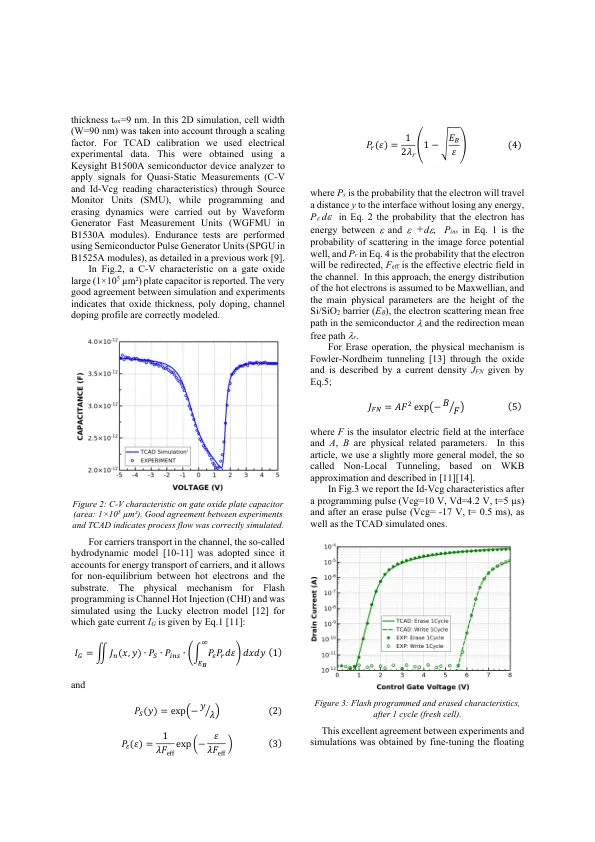

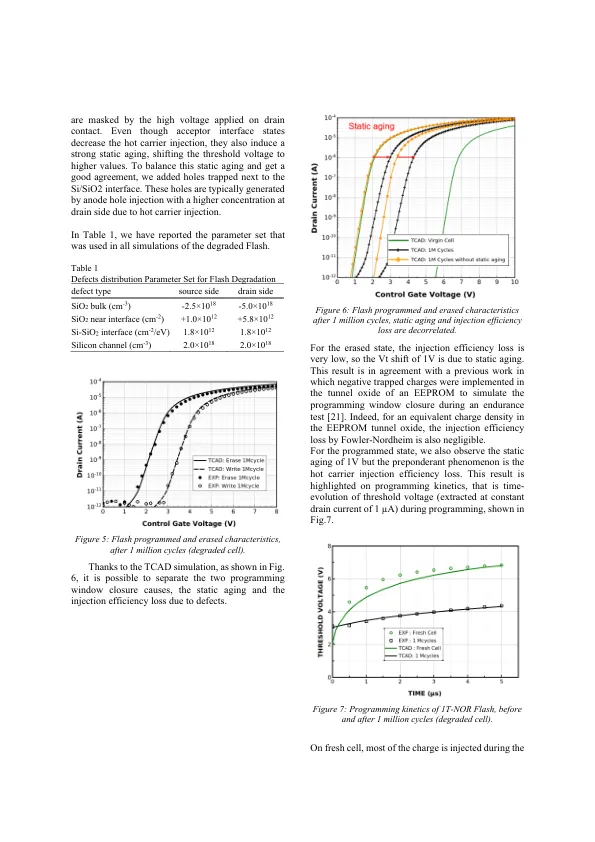

a 意法半导体,法国鲁塞 b 艾克斯-马赛大学,CNRS,IM2NP,13451 马赛,法国 摘要 在本文中,我们对 100 万次编程/擦除 (P/E) 操作后的 1T-NOR 闪存电气特性进行了 TCAD 模拟。由于 TCAD 模拟,提出了空间缺陷分布来解释耐久性下降的原因。工艺模拟基于意法半导体生产的 90 nm 节点嵌入式非易失性存储器技术 (eNVM)。编程和擦除期间使用热载流子注入 (HCI) 和高级隧道模型,而闪存性能下降则通过位于 Si/SiO 2 界面和 SiO 2 内部的缺陷来考虑。获得的循环前后编程窗口以及消耗电流的结果与实验结果高度一致。此外,在此框架内,可以正确重现 100 万次循环后无应力闪存侧的 IV 特性,如文献中先前报道的那样。 1. 引言电荷存储浮栅存储器Flash-EEPROM(电可擦除可编程只读存储器)或简称Flash,可以说是迄今为止市场上最成功的非易失性存储器之一,每年仍有数十亿个单元被处理,预计到2028年,复合年增长率(CGAR)将达到14.4% [1]。它的可靠性(主要包括耐用性和数据保留率)在过去几十年中得到了广泛的研究[2-4]。在本文中,我们使用技术计算机辅助设计(TCAD)来模拟100万次循环后的1T-NOR闪存编程窗口关闭。TCAD是一种基于物理的数值建模方法,用于精确模拟微电子器件的制造工艺和电气特性,该工具已成功用于器件性能优化和可靠性提高[5,6,7]。与[8]类似,Flash耐用性是通过缺陷建模的;然而,在本文中,我们采用了 Si/SiO 2 界面和 SiO 2 体氧化物中的非均匀缺陷分布以及不同类型的缺陷。这种方法与 [4] 中报道的实验结果一致。

耐久性下降后的 1T-NOR 闪存

主要关键词