机构名称:

¥ 1.0

I.在非常大规模集成(VLSI)设计领域的介绍中,全球路由的效率和可靠性在综合电路(ICS)的整体性能中起关键作用。随着IC的复杂性继续随着技术的发展而增长,传统的路由算法在适应现代芯片布局的复杂和动态性质方面面临着越来越多的挑战。这些算法通常基于静态规则和启发式方法,可能会导致次优路径,从而导致线长度增加,信号延迟更高和拥挤。这种拥塞反过来可以显着影响最终芯片设计的性能,功耗和面积。为了应对这些挑战,对将先进的机器学习技术(尤其是深度学习)应用于VLSI全球路线的拥堵预测问题越来越兴趣。深度学习提供了学习大型数据集中复杂模式和依赖关系的潜力,使其非常适合预测和减轻VLSI设计环境中的拥塞。通过利用深度学习模型,可以开发一种动态路由优化方法,以适应实时设计条件和路由模式。

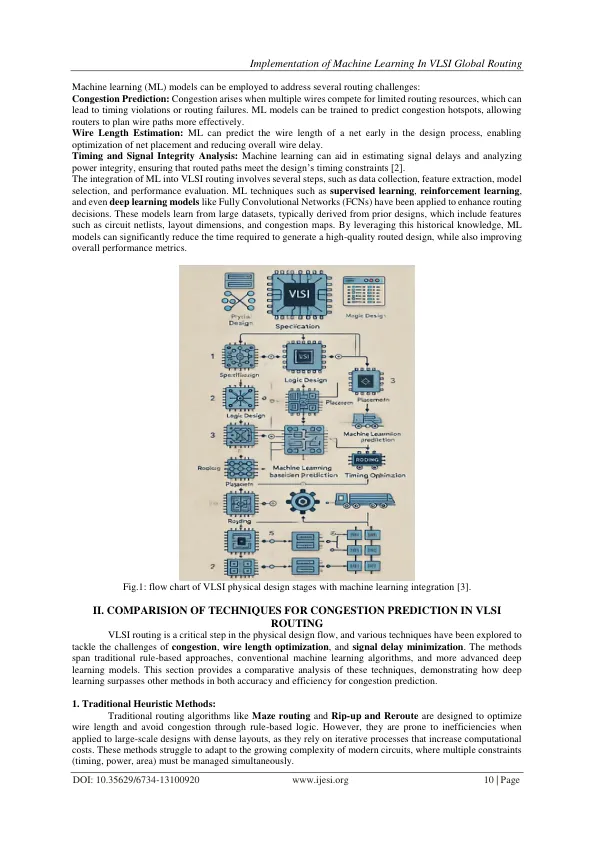

在VLSI全局路由中实施机器学习

主要关键词