机构名称:

¥ 1.0

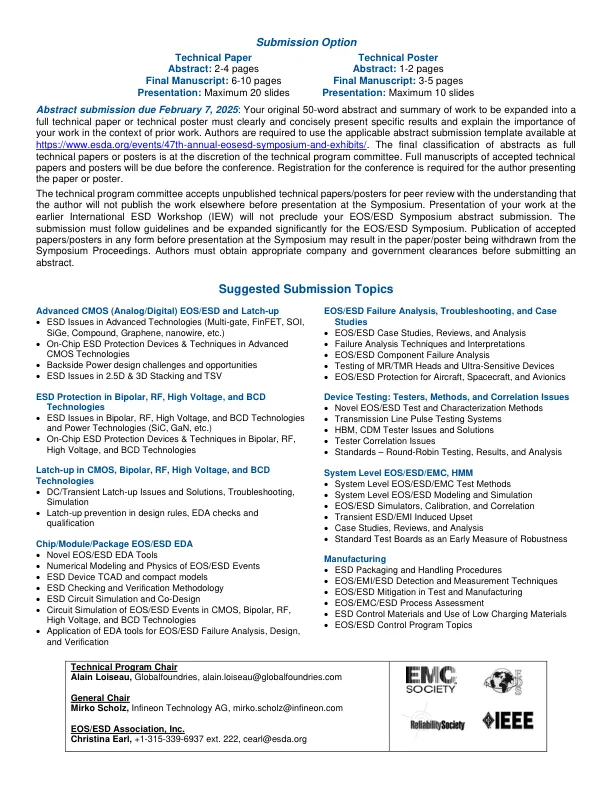

特殊焦点模块背面功率,3D集成,内存堆叠,异源集成(启用AI革命)新兴技术CMOS Technologies的缩放范围继续延伸,超出了当前3 nm节点的清晰外观,包括围绕技术周围的闸门。引入背部功率将为高级技术带来令人兴奋的新功能,但同时,带来了在提供的ESD设备中需要解决的新ESD挑战。使用高级技术,高应用程序性能和异质集成概念为ESD保护设计带来了新的挑战。对于2025年EOS/ESD研讨会,我们正在寻找展示技术层面的进步和挑战的原始出版物。设备测试技术缩放和包装的复杂性的增加需要更高级的ESD测试解决方案。现代包装技术还引入了制造过程中未知的ESD应力水平。初始测量结果显示出非常快的脉冲解决了次纳秒时间域。现有的测试方法适合在此时间域中的表征,还是我们需要新的方法?我们邀请提交这些问题以及在ESD测试其他领域的进步。制造控制商业高性能2.5D和3D IC的制造具有与ESD相关的特定挑战,其中包含新材料,自定义集成和相关测试方法的新组装过程。模具到磁力,晶圆到磁力粘结,堆叠的ICS和模块包括具有低ESD承受能力的子系统,具有大量和各种各样的模具到die接口和小凹凸音高。我们邀请提交的意见,以解决控制和处理方面的进步,以朝着低于5 V制度的ESD稳健性非常低的行业趋势。

2025请致电论文

主要关键词