机构名称:

¥ 1.0

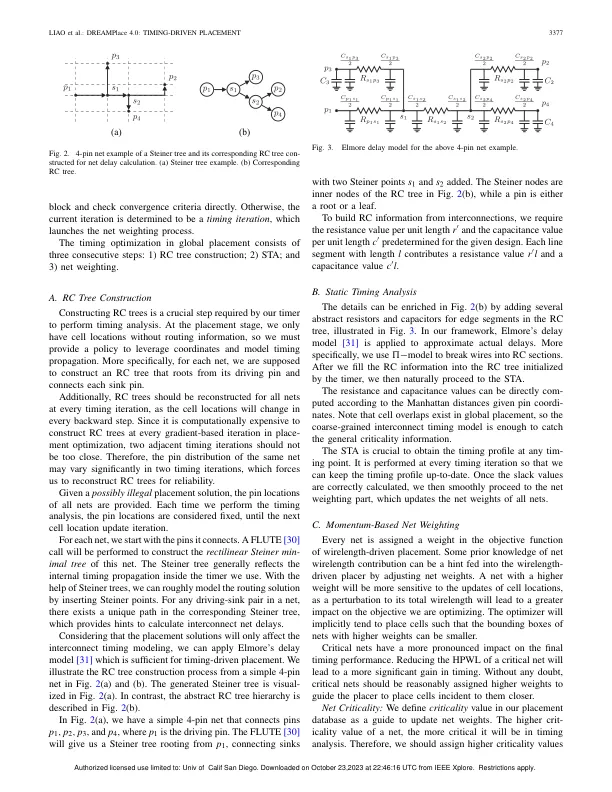

I. i ntroduction c ircuit放置是一个重要的VLSI设计阶段。放置的目的是在给定的芯片布局上找到电路组件的最佳位置[2]。的放置通常被放置为数学优化问题,其功能可将电路组件之间互连成本的成本降至最低。在大多数以前的位置框架中,互连成本是由所有网的总线索建模的,所有网的总线长度是由半渗透线(HPWL)估算的或其他近似值。除了仅是一个大约涉及的情况外,总的线长对所有网络都同样关注,而不是专注于关键的临界网和路径。这与定时驱动的放置相反,该位置特定针对电线关键路径,通常会产生立即的电路性能受益。的放置可以分为全局位置阶段和详细的位置阶段,并且可以将正时优化应用于两个阶段。按时驱动的全球位置的目标是实现大致不错的负面懈怠

Dreamplace 4.0:基于动量的净重和基于拉格朗日的精炼的时序驱动的位置