机构名称:

¥ 1.0

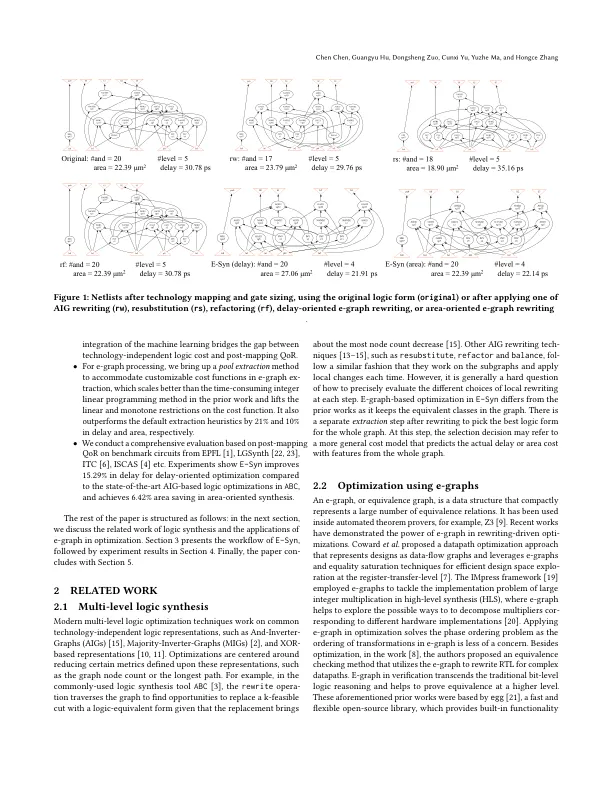

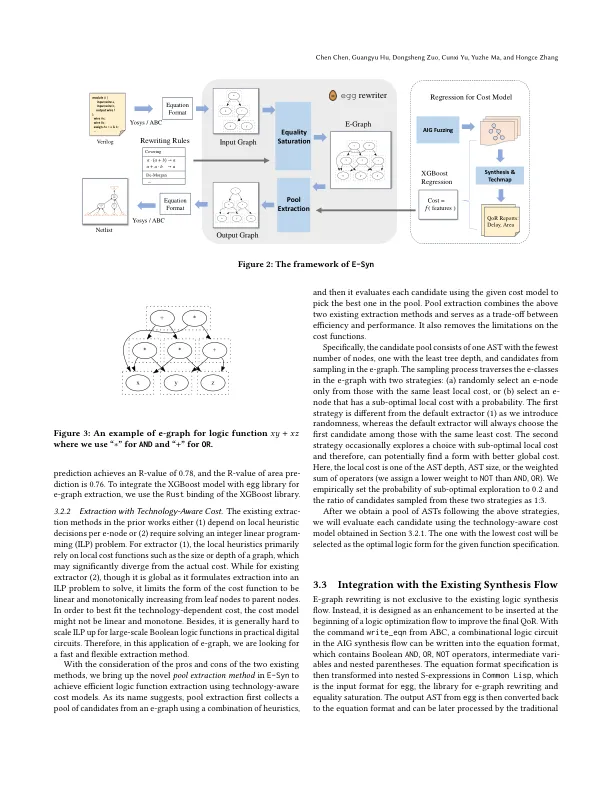

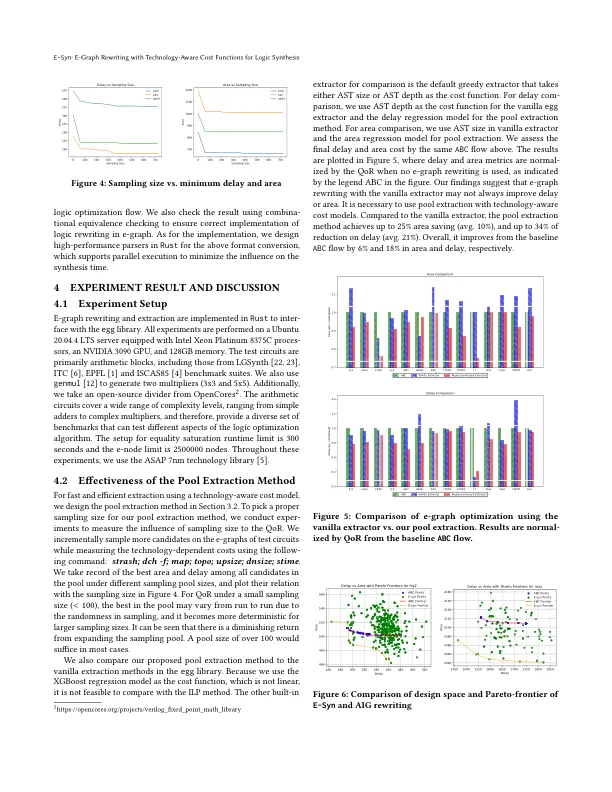

逻辑合成在数字设计流中起着至关重要的作用。它对电路实现的最终结果质量(QOR)具有决定性的影响。但是,现有的多级逻辑优化算法通常采用一系列局部优化步骤采用贪婪的方法。每个步骤将电路分为小块(例如,可行的切割),并分别对单个零件进行增量更改。这些本地优化步骤可能会限制勘探空间,并可能错过重大改进的机会。为了解决限制,本文提出了在逻辑合成中使用电子图像。新的工作流(名为e-Syn)利用良好的电子支柱基础架构有效地执行逻辑重写。它探讨了一套等效的布尔表示,同时允许技术意识到的成本功能更好地支持面向延迟和面积的逻辑合成。在广泛的基准设计上进行的实验表明,与常用的基于AIG的逻辑合成流相比,我们提出的逻辑选择方法达到了更广泛的设计空间。它可以在平均年龄15.29%的延迟延迟延迟延迟延迟,以节省面积为导向的合成的6.42%面积。

e-syn:通过技术意识到的逻辑综合成本功能重写

主要关键词