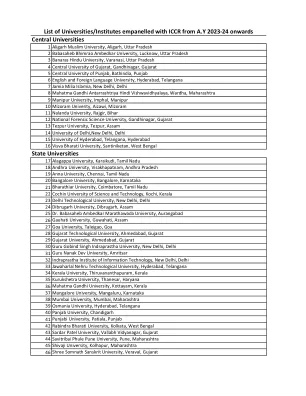

机构名称:

¥ 1.0

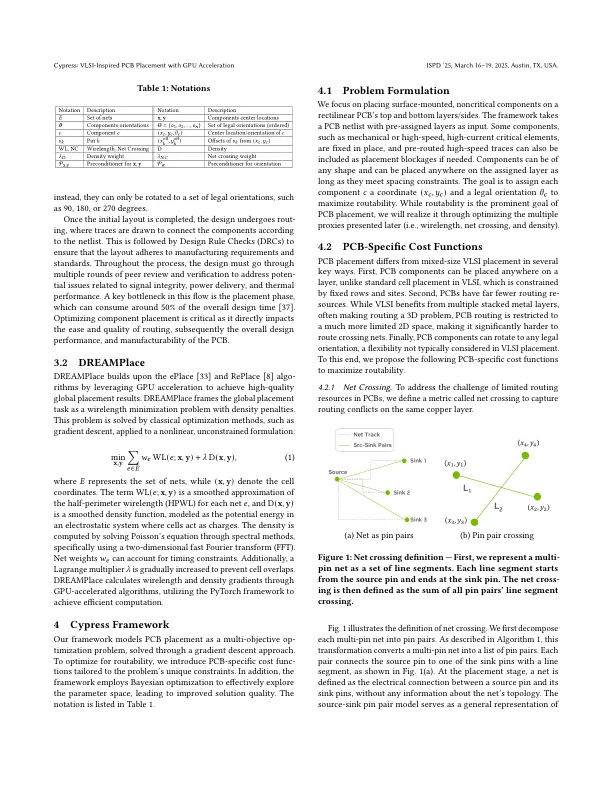

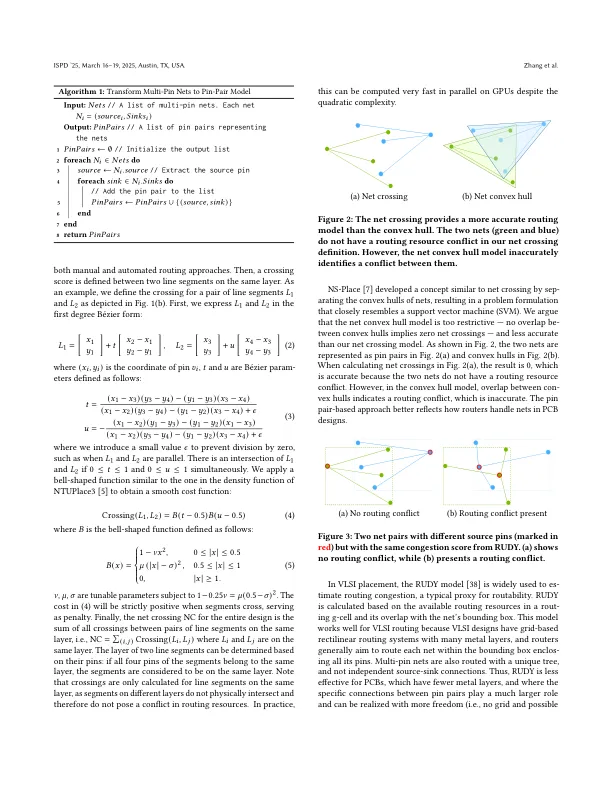

印刷电路板(PCB)设计的规模已大大提高,现代商业设计具有10,000多个组件。但是,放置过程大大依赖了需要数周完成的手动努力,强调了对自动PCB放置方法的需求。PCB放置的挑战来自其灵活的设计空间和有限的路由资源。现有的自动PCB放置工具在质量和可扩展性方面取得了有限的成功。相比之下,非常大规模的集成(VLSI)放置方法已被证明是可扩展的,对于具有数百万个细胞并提供高质量结果的设计是可扩展的。因此,我们提出了柏树,这是一种受VLSI启发的可扩展的,加速的PCB放置方法。它结合了适合PCB布局的量身定制的成本功能,约束处理和优化的技术。此外,对现实和开源基准的需求不断增长,以(1)在工具和(2)建立Performance基准之间进行有意义的比较以跟踪PCB放置技术的进度。为了解决这一差距,我们提出了一个从实际商业设计中合成的PCB基准套件。我们使用基准套件来评估针对最先进的商业和学术PCB放置工具的方法。我们的方法在提出的基准测试标准上证明了1-5.9倍的可路由。对于完全路由的设计,赛普拉斯达到了1-19.7×较短的路由轨道长度。随着GPU加速度,柏树在运行时间内最多可提供492.3倍的加速。最后,我们展示了对真实商业设计的可扩展性,这是现有工具无与伦比的功能。

赛普拉斯:带有GPU加速度的VLSI启发的PCB放置

主要关键词