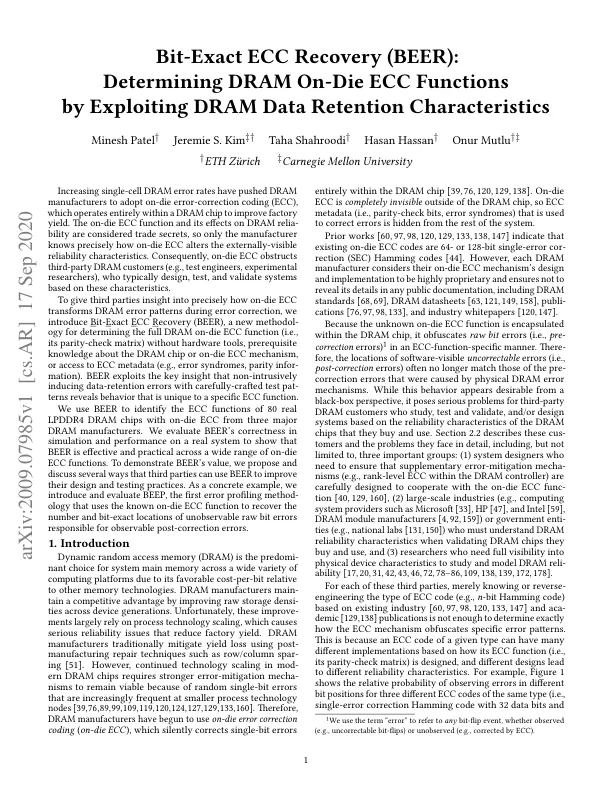

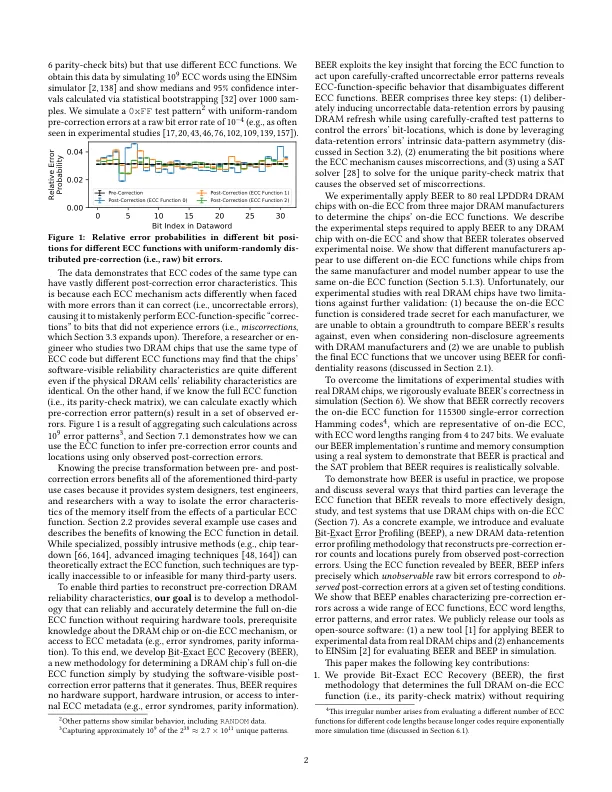

单单元 DRAM 错误率的不断上升促使 DRAM 制造商采用片上纠错编码 (ECC),该编码完全在 DRAM 芯片内运行,以提高工厂产量。片上 ECC 功能及其对 DRAM 可靠性的影响被视为商业机密,因此只有制造商才知道片上 ECC 如何改变外部可见的可靠性特性。因此,片上 ECC 阻碍了第三方 DRAM 客户(例如测试工程师、实验研究人员),他们通常根据这些特性设计、测试和验证系统。为了让第三方准确了解片上 ECC 在错误校正过程中如何转换 DRAM 错误模式,我们引入了比特精确 ECC 恢复 (BEER),这是一种无需硬件工具、无需有关 DRAM 芯片或片上 ECC 机制的先决知识或无需访问 ECC 元数据(例如错误综合征、奇偶校验信息)即可确定完整 DRAM 片上 ECC 功能(即其奇偶校验矩阵)的新方法。BEER 利用了关键洞察,即使用精心设计的测试模式非侵入式地诱导数据保留错误会揭示特定 ECC 功能所独有的行为。我们使用 BEER 来识别来自三大 DRAM 制造商的 80 个带有片上 ECC 的真实 LPDDR4 DRAM 芯片的 ECC 功能。我们评估了 BEER 在模拟中的正确性和在真实系统上的性能,以表明 BEER 在各种片上 ECC 功能中都是有效且实用的。为了证明 BEER 的价值,我们提出并讨论了第三方可以使用 BEER 来改进其设计和测试实践的几种方法。作为一个具体的例子,我们介绍并评估了 BEEP,这是第一种错误分析方法,它使用已知的片上 ECC 功能来恢复导致可观察的后校正错误的不可观察的原始位错误的数量和位精确位置。1. 简介动态随机存取存储器 (DRAM) 是各种计算平台上系统主存储器的主要选择,因为它相对于其他存储器技术具有优惠的每位成本。DRAM 制造商通过提高设备代之间的原始存储密度来保持竞争优势。不幸的是,这些改进很大程度上依赖于工艺技术的扩展,这会导致严重的可靠性问题,从而降低工厂产量。DRAM 制造商传统上使用行/列备用等制造后修复技术来减少产量损失 [51]。然而,现代 DRAM 芯片技术的不断扩展需要更强大的错误缓解机制才能保持可行性,因为在较小的工艺技术节点上,随机单比特错误越来越频繁 [39,76,89,99,109,119,120,124,127,129,133,160]。因此,DRAM 制造商已经开始使用片上纠错编码(片上 ECC),它可以悄悄地纠正单比特错误

位精确 ECC 恢复 (BEER):确定 DRAM 开启...

主要关键词