机构名称:

¥ 1.0

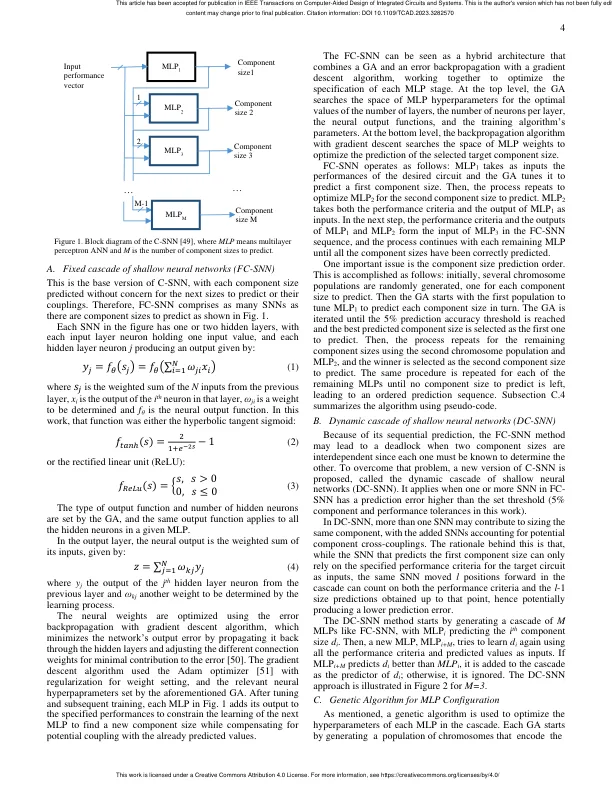

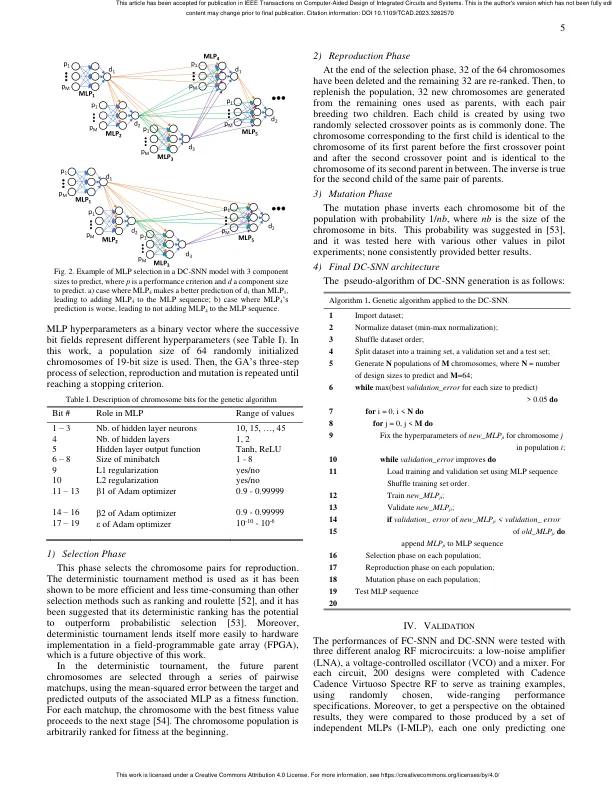

摘要 - 提出了用于模拟电路组件自动尺寸的深神经网络体系结构,重点是2至5 GHz区域的射频(RF)应用。它解决了通常少数网络培训示例的挑战和多种解决方案的存在,其中该型解决方案是集成电路实现的不切实际值。,由于一系列专用的浅神经网络(SNN),我们通过一次将学习限制到一个组件大小来解决这些问题,在该级联限制了下一个网络的预测。此外,SNN是通过遗传算法单独调整预测顺序和准确性的。在每个步骤中的解决方案空间的缩小允许使用小型训练集,以及SNNS处理组件相互依赖的限制。该方法在三种不同类型的RF微电路上成功验证:低噪声放大器(LNA),电压控制的振荡器(VCO)和混合器,使用180 nm和130 nm CMOS实现。所有预测均在成分和性能水平的真实值的5%之内,所有响应均在4至47分钟后在不到5 s的情况下获得。在常规PC站进行培训。获得的结果表明,所提出的方法快速且适用于任意模拟电路拓扑,而无需为每组新的所需电路性能重新训练开发的神经网络。

通过浅神经网络级联的模拟RF电路尺寸

主要关键词