机构名称:

¥ 1.0

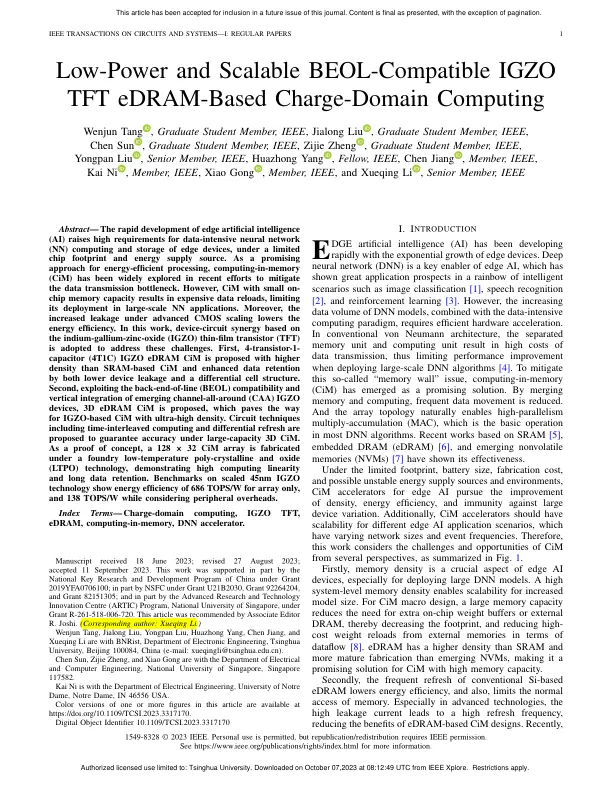

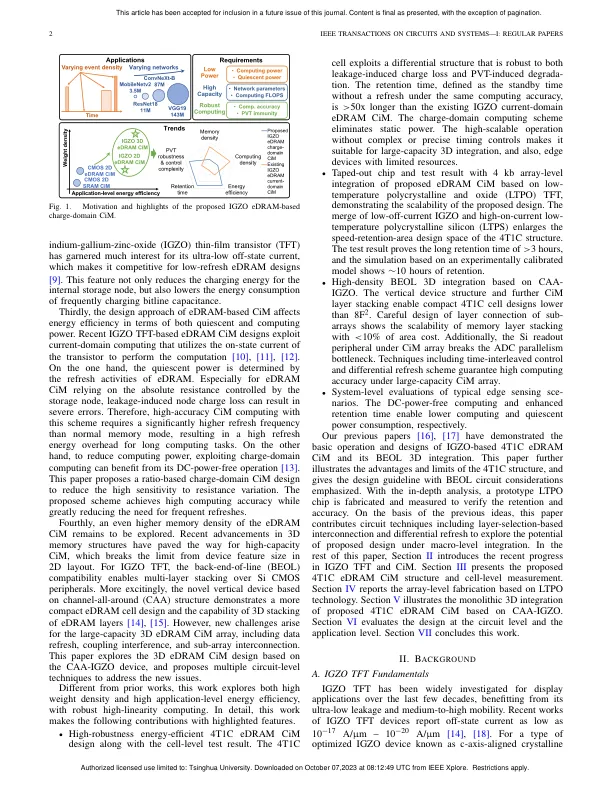

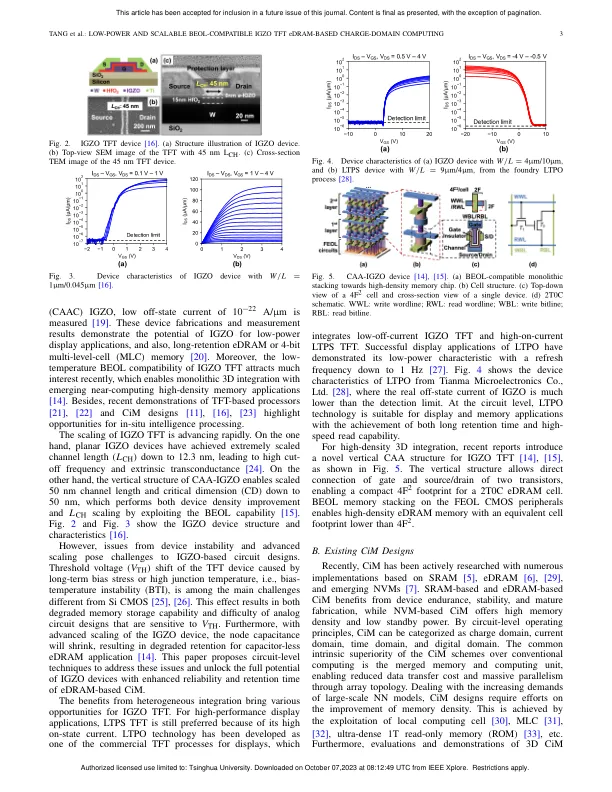

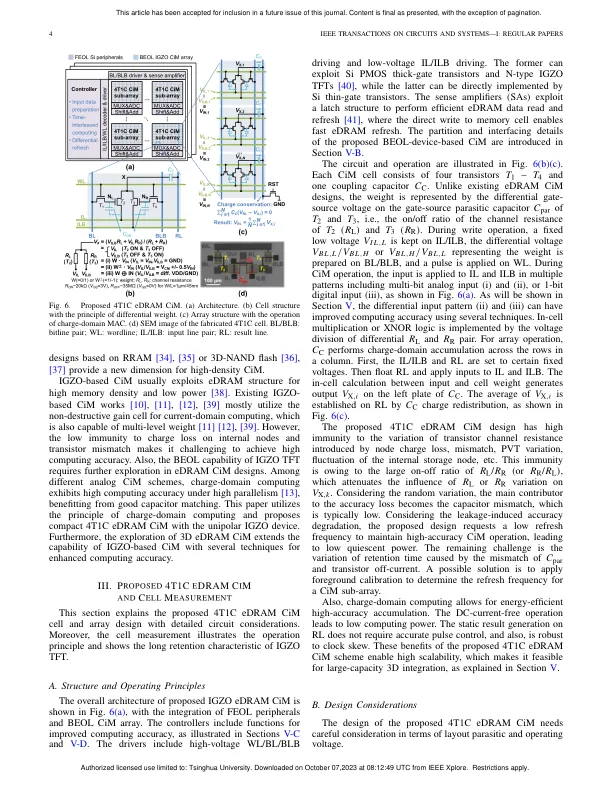

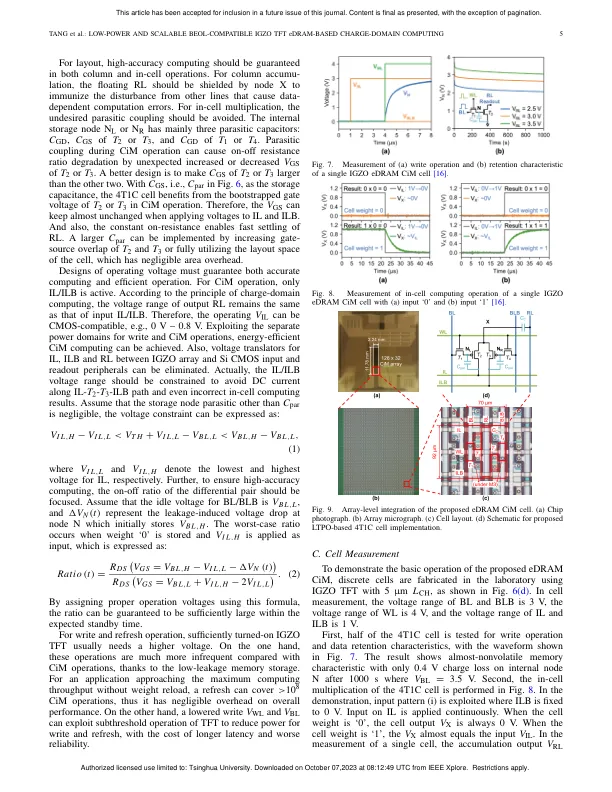

摘要 — 在有限的芯片占用空间和能源供应下,边缘人工智能 (AI) 的快速发展对边缘设备的数据密集型神经网络 (NN) 计算和存储提出了很高的要求。作为一种有前途的节能处理方法,内存计算 (CiM) 近年来在缓解数据传输瓶颈的努力中得到了广泛的探索。然而,片上内存容量较小的 CiM 会导致昂贵的数据重新加载,限制了其在大规模 NN 应用中的部署。此外,先进 CMOS 缩放下增加的泄漏降低了能源效率。在本文中,采用基于铟镓锌氧化物 (IGZO) 薄膜晶体管 (TFT) 的器件电路协同来应对这些挑战。首先,提出了 4 晶体管 1 电容器 (4T1C) IGZO eDRAM CiM,其密度高于基于 SRAM 的 CiM,并且通过较低的器件泄漏和差分单元结构增强了数据保留。其次,利用新兴全通道 (CAA) IGZO 器件的后端 (BEOL) 兼容性和垂直集成,提出了 3D eDRAM CiM,为基于 IGZO 的超高密度 CiM 铺平了道路。提出了包括时间交错计算和差分刷新在内的电路技术,以保证大容量 3D CiM 下的准确性。作为概念验证,在代工厂低温多晶和氧化物 (LTPO) 技术下制造了一个 128 × 32 CiM 阵列,展示了高计算线性度和长数据保留时间。在扩展的 45nm IGZO 技术上的基准测试显示,仅阵列的能效为 686 TOPS/W,考虑外围开销时为 138 TOPS/W。

低功耗、可扩展、兼容 BEOL 的 IGZO TFT eDRAM 电荷域计算

主要关键词