机构名称:

¥ 1.0

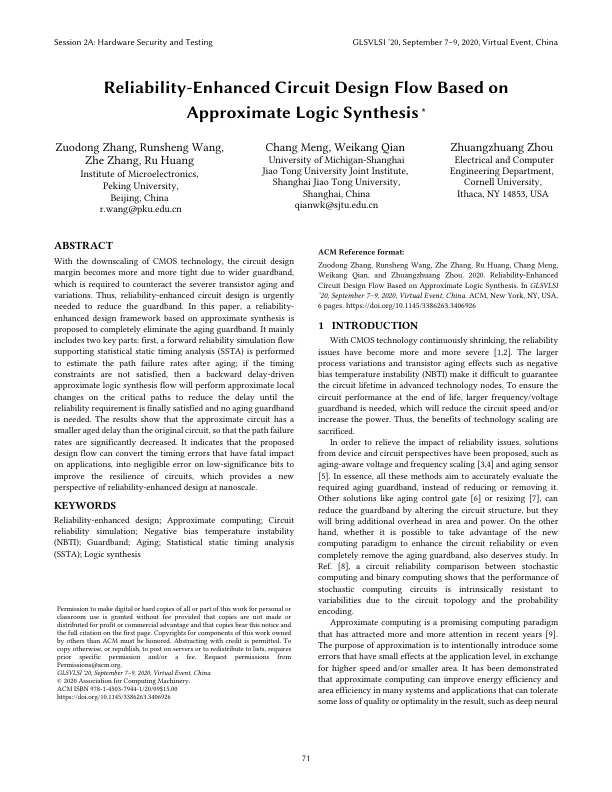

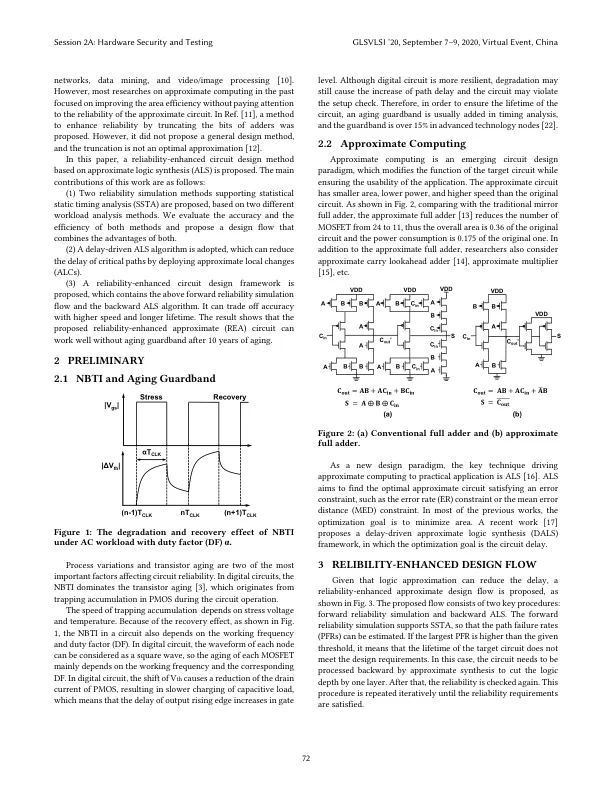

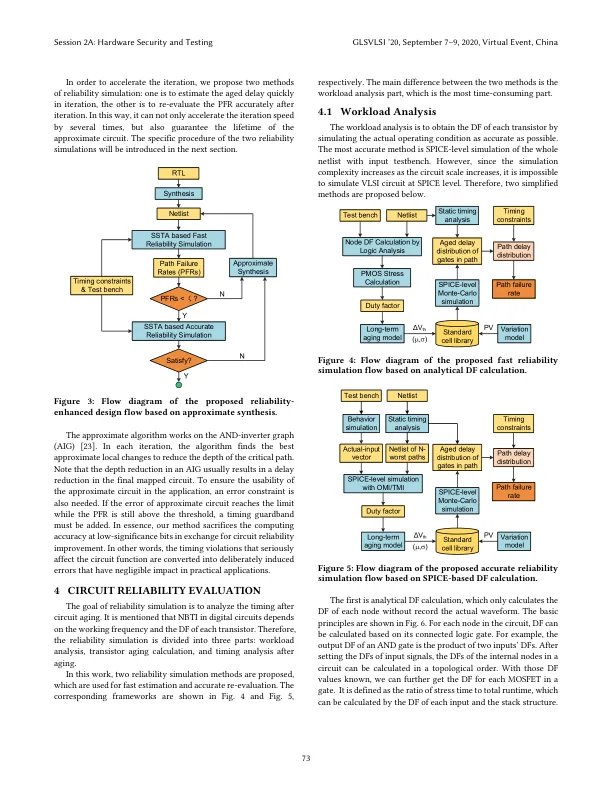

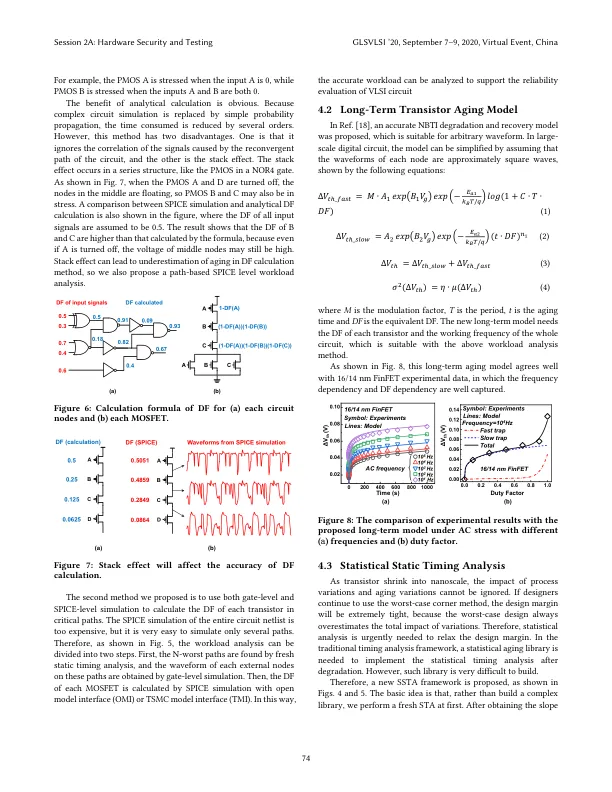

随着CMOS技术的缩小缩放,由于更宽的防护带,电路设计的边缘变得越来越紧,这是抵消更严重的晶体管老化和变化所必需的。因此,迫切需要可靠性增强的电路设计来减少护栏。在本文中,提出了一个基于近似合成的可靠性增强的设计框架,以完全消除衰老的后卫带。它主要包括两个关键部分:首先,进行远期可靠性模拟流支持统计静态时序分析(SSTA)以估计老化后的路径故障率;如果不满足正时约束,则向后延迟驱动的近似逻辑合成流将在关键路径上进行近似局部变化,以减少延迟,直到最终满足可靠性要求并且不需要老化的护罩带。结果表明,近似电路的老化延迟小于原始电路,因此路径故障率显着降低。表明,提出的设计流可以将对应用产生致命影响的时间误差转换为低显着性位上可忽略的错误,以提高电路的弹性,这为纳米级的可靠性增强设计提供了新的视角。

可靠性增强电路设计流基于近似逻辑合成 *

主要关键词