机构名称:

¥ 1.0

摘要 - 电子产品越来越容易受到硅内能量颗粒相互作用的影响。为了在辐射效应下提高电路可靠性,在VLSI系统的设计流中采用了几种硬化技术。本文提出了逻辑门中的PIN分配优化,以减少单个事件瞬态(SET)横截面并提高轨内软率。信号概率传播用于通过重新交换或引脚交换将最低概率分配给电路最敏感的输入组合。细胞优化的软率最高可降低48%。对于分析的算术基准电路,优化的细胞网列在设置的横截面和轨内软校正速率上可以在电路设计区域内无需成本降低8%至28%。另外,由于引脚交换是一种布局友好的技术,因此优化不会影响细胞放置,并且可以与逻辑和物理合成中的其他硬化技术一起采用。

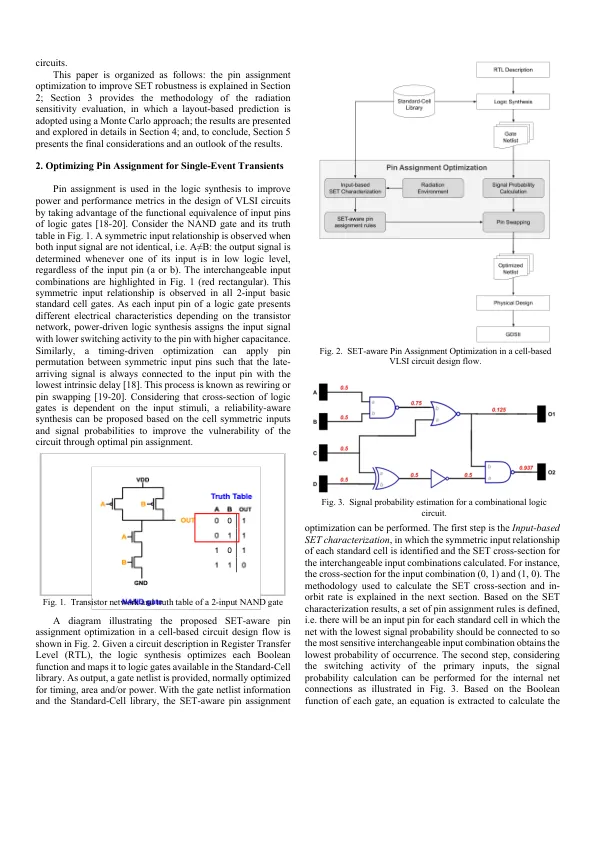

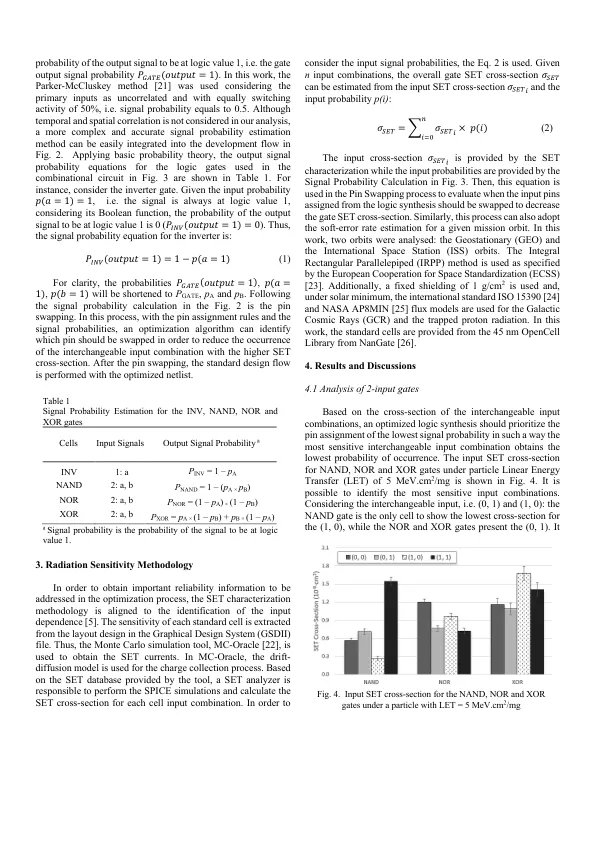

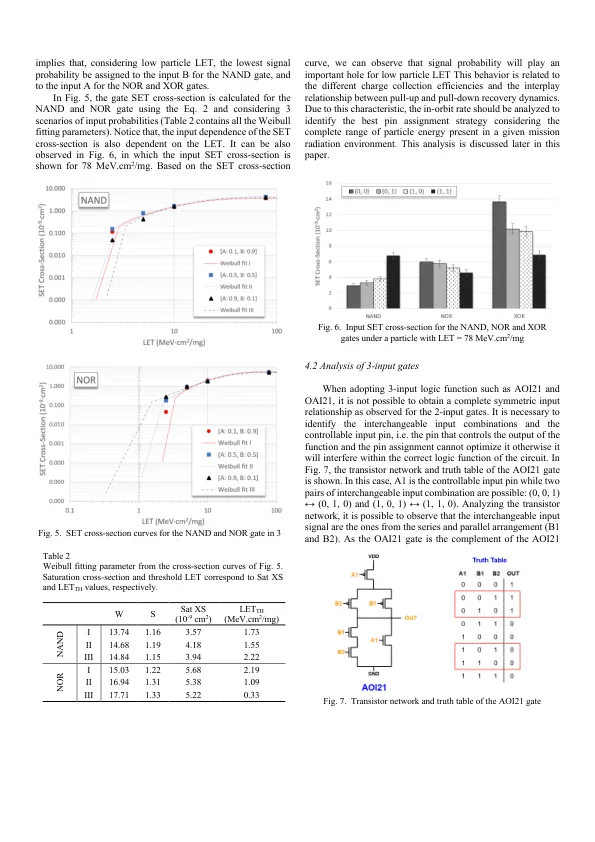

可靠性驱动的PIN分配优化以改进...