机构名称:

¥ 1.0

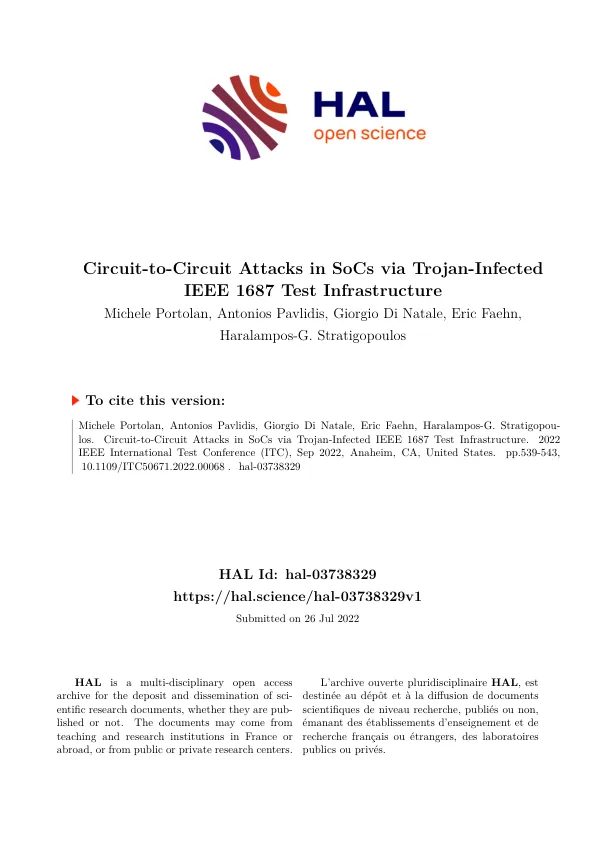

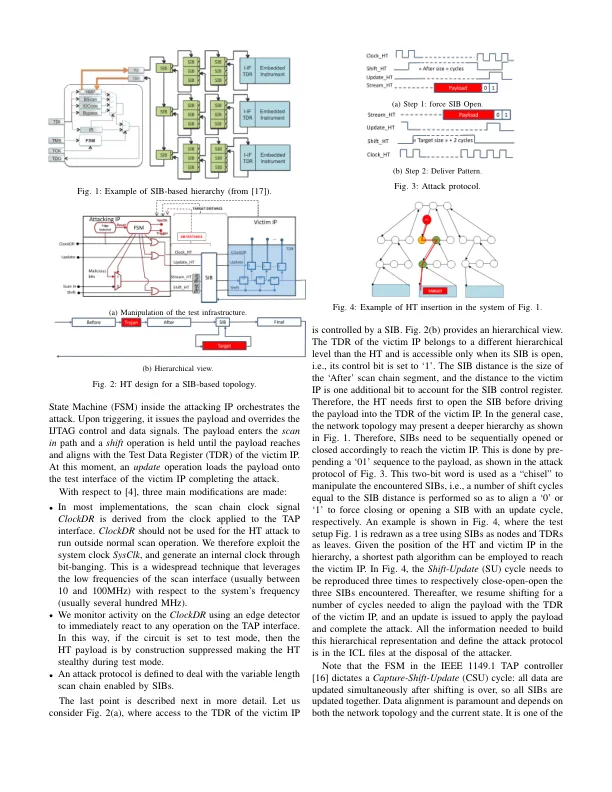

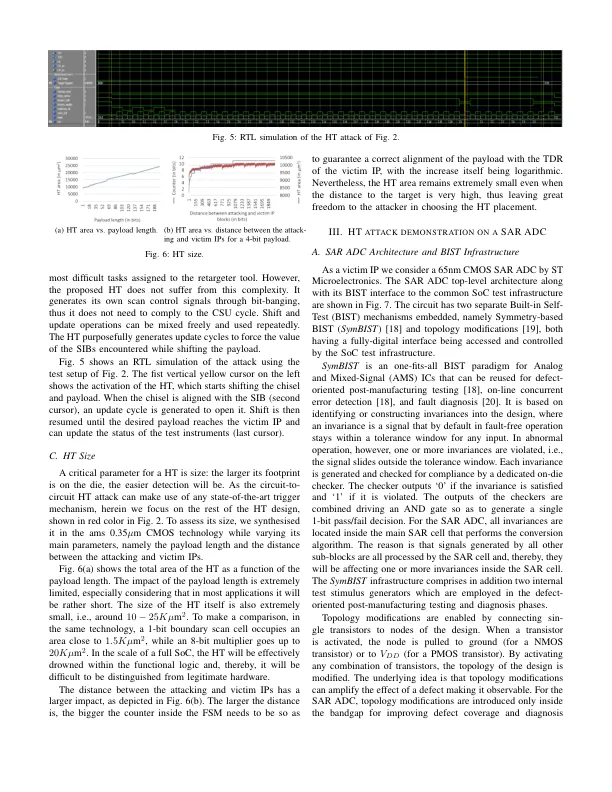

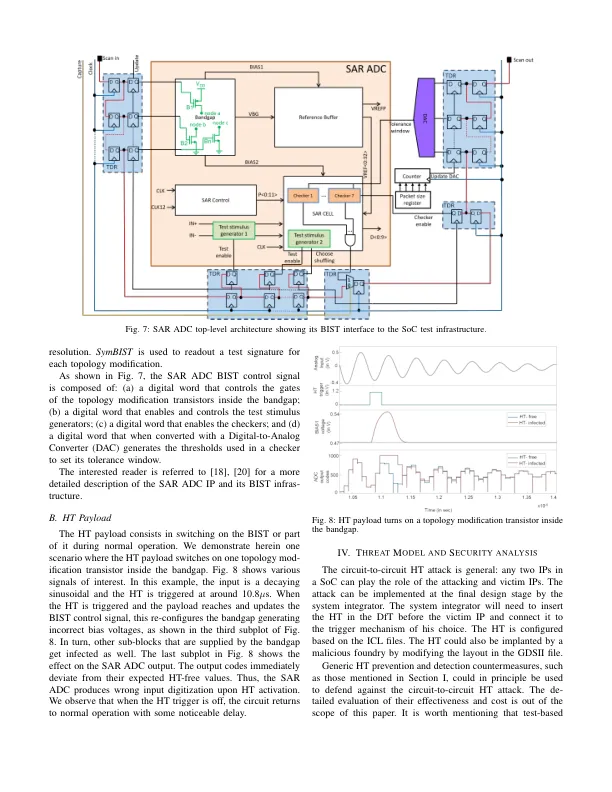

硬件木马 (HT) 是对集成电路 (IC) 的恶意修改。它由触发器和有效载荷机制组成。触发器定义激活时间(即始终开启、满足罕见条件时、基于时间、外部),有效载荷是激活的 HT 对受害 IC 的影响(即信息泄露、性能下降、拒绝服务)。HT 可以插入到设计过程的任何阶段和任何抽象级别,并且可以位于芯片上的任何位置 [1]。从攻击者的角度来看,目标是使 HT 隐秘且占用空间小,以逃避检测。HT 设计变得越来越复杂 [2]–[4],使得制定对策非常具有挑战性。对策包括在硅片生产前防止 HT 插入(即基于功能填充单元 [5]、逻辑混淆 [6]、伪装 [7] 或拆分制造 [8])、在 IC 使用前检测 HT 的存在(即基于逻辑测试工具 [9]、信息流跟踪 (IFT) [10] 和侧信道分析 [11]、[12])以及在运行时检测 HT 激活(即基于片上监视器 [13])。在本文中,我们演示了一种 HT 设计,该设计利用可测试设计 (DfT) 基础设施在片上系统 (SoC) 内部实施电路到电路攻击。HT 隐藏在 SoC 的“攻击”知识产权 (IP) 核内,一旦激活,它就会以恶意位模式的形式生成有效载荷。有效载荷进入测试访问机制的扫描链,该扫描链遍历 SoC 并控制嵌入在 IP 内的测试仪器。 HT 操纵扫描链,在目标受害者 IP 的接口上传播有效载荷。有效载荷会更新受害者 IP 内部测试仪器的状态,将其设置为部分和未记录的测试模式,从而破坏其在正常运行模式下的功能。电路到电路 HT 攻击属于更广泛的扫描攻击类别

通过受木马感染的 IEEE 1687 测试基础设施对 SoC 进行电路到电路攻击

主要关键词