机构名称:

¥ 1.0

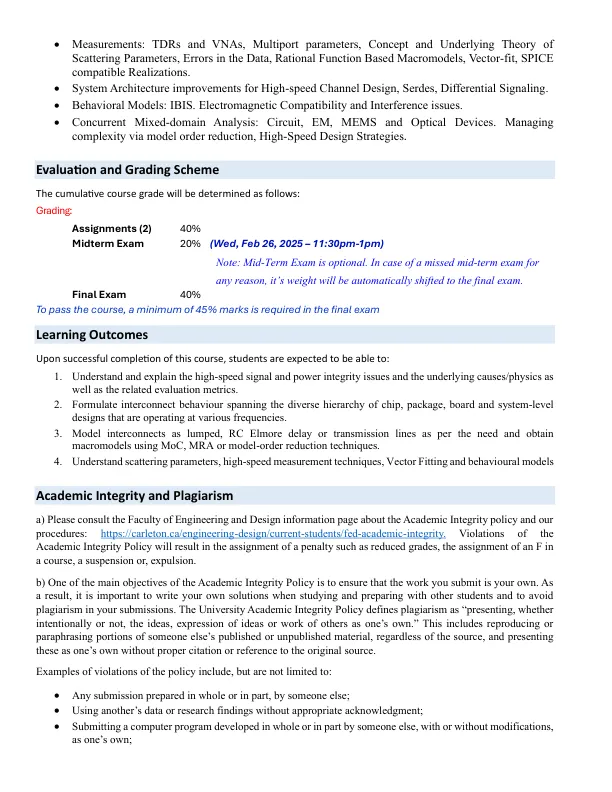

课程描述:高速低功耗设计中的串扰、失真、延迟、衰减、地面反弹、趋肤效应、抖动、符号间干扰的基础知识。建模/仿真:高速互连、封装、接地/电源平面、通孔、PCB 和 3D-IC;眼图、Elmore 延迟、有损耦合、传输线、电报方程、线路参数提取、测量参数。宏建模:无源性/因果关系、特征法、矩阵有理近似、矢量拟合、模型降阶、电磁兼容性/干扰、混合域系统和基于多物理的并发分析。先决条件:就读卡尔顿大学电子/SCE 系或 OCIECE 的研究生课程或经系批准。讲座:每周三小时 VLSI 电路技术的快速发展,加上复杂/微型设备的趋势,对专注于微电子的计算机辅助设计 (CAD) 工具提出了巨大的需求。设计要求变得非常严格,要求更高的运行速度、更尖锐的激励、更密集的布局和低功耗。因此,延迟、衰减、串扰、地弹等信号完整性问题正在成为高速电路和系统设计和验证的主要瓶颈。如果在设计阶段没有正确处理高速效应,可能会导致逻辑故障,导致制造的数字电路无法运行,或者扭曲模拟信号,使其无法满足规格。由于 VLSI 设计周期中的额外迭代成本极高,因此准确预测这些影响是高速设计中的必需品。设计和 CAD 社区目前正在发生范式转变,以适应高速设计问题的新要求。然而,目前可用的 CAD 工具和设计策略无法充分处理涵盖不同领域的复杂高速电路设计/分析场景。本课程旨在涵盖高速设计、对根本原因的理解、相关物理和高速互连建模/仿真/设计方法。讲师:

2025 年冬季

主要关键词