机构名称:

¥ 1.0

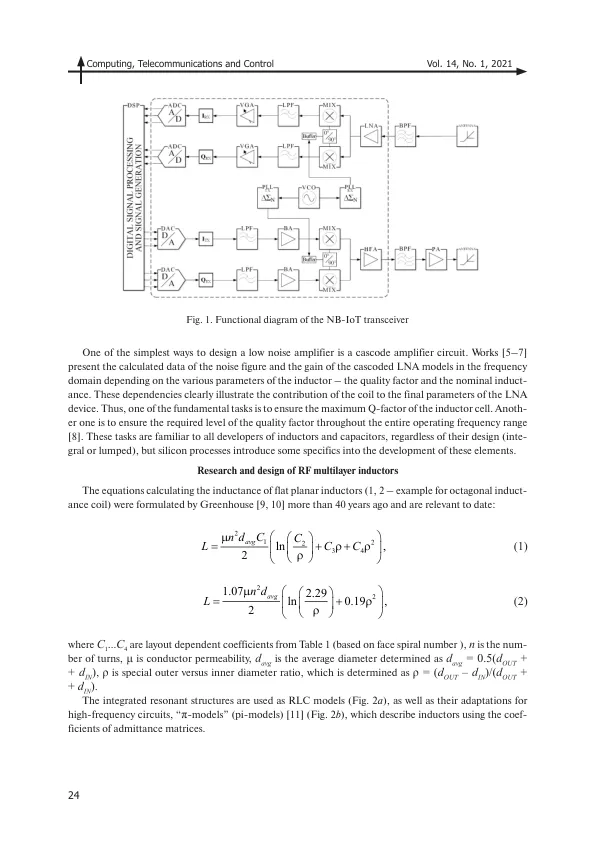

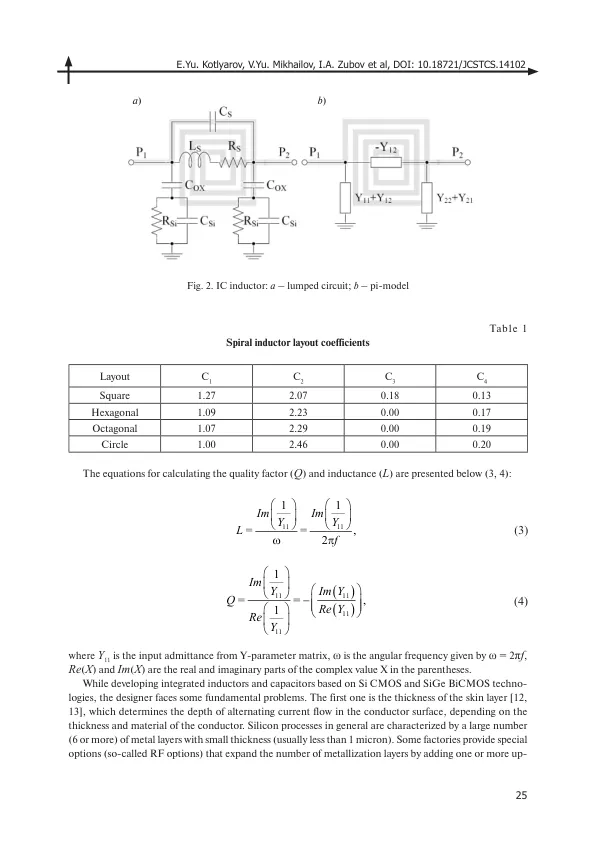

本工作致力于微波路径平面元件开发的某些方面,这些元件用于低噪声 LTE 范围放大器的设计,即电感器,以便进一步用作 NB-IoT 收发器的一部分。给出了高频电感器设计的一般理论计算。以标称值为 7 nH 的多层 CMOS 90 nm 电感器为例,我们通过电磁 (EM) 模型展示了通过复制层获得的结构厚度的影响,该结构厚度用于获得所需的表皮层厚度并在 0.5 至 3.5 GHz 的 LTE 频率范围内实现最佳品质因数。为了更好地理解电感器的工作原理,比较了针对不同基板电导率值进行 EM 模拟所获得的模型。获得的数据部分反驳了通过使用多个 TSV 阵列组合一组硅工艺堆栈的上部金属来增加电感器最大厚度的必要性。由于基板对电感器下部金属层的电容影响不断增大,尽管趋肤效应对低频有负面影响,但仍可以通过具有最少金属层的结构来实现最高的Q值和自谐振频率。

接收、发射和...的电路和系统

主要关键词