机构名称:

¥ 1.0

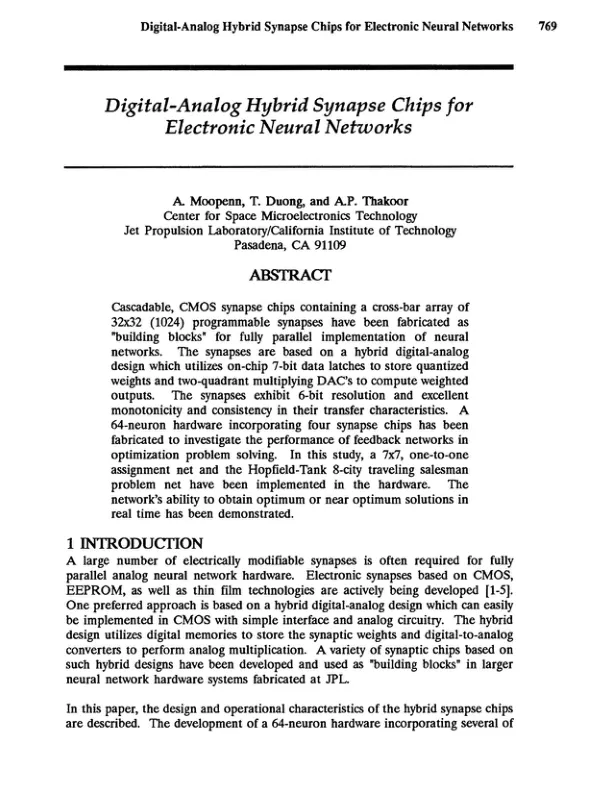

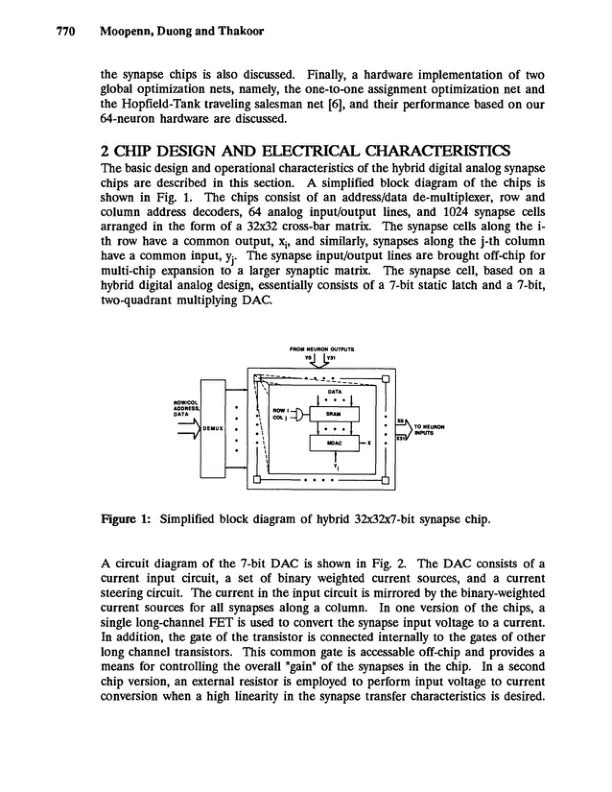

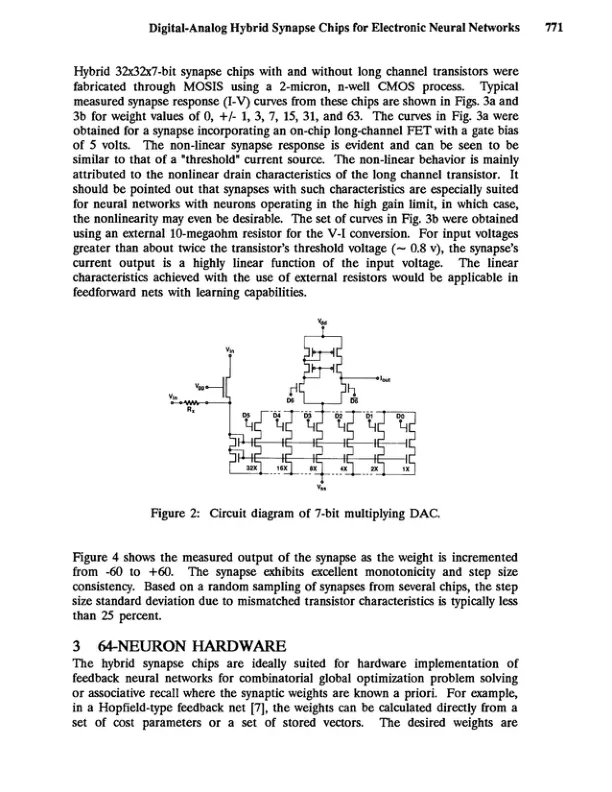

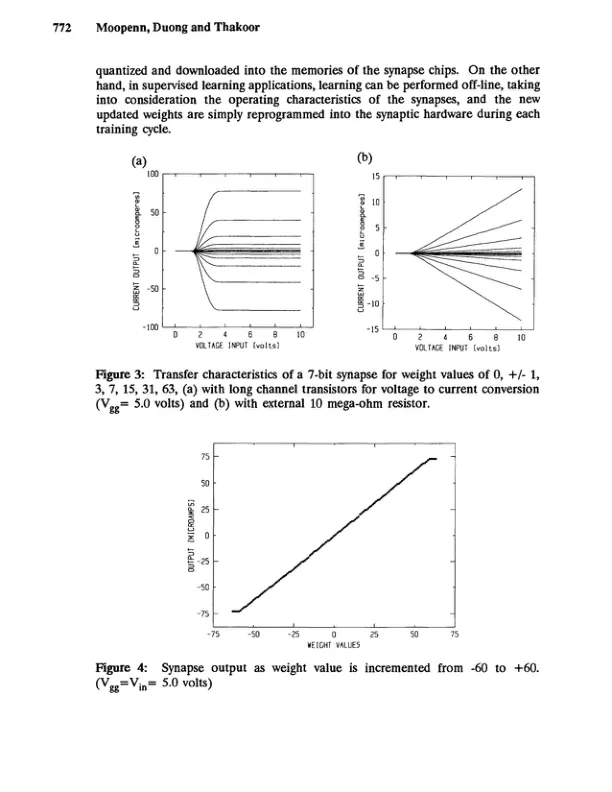

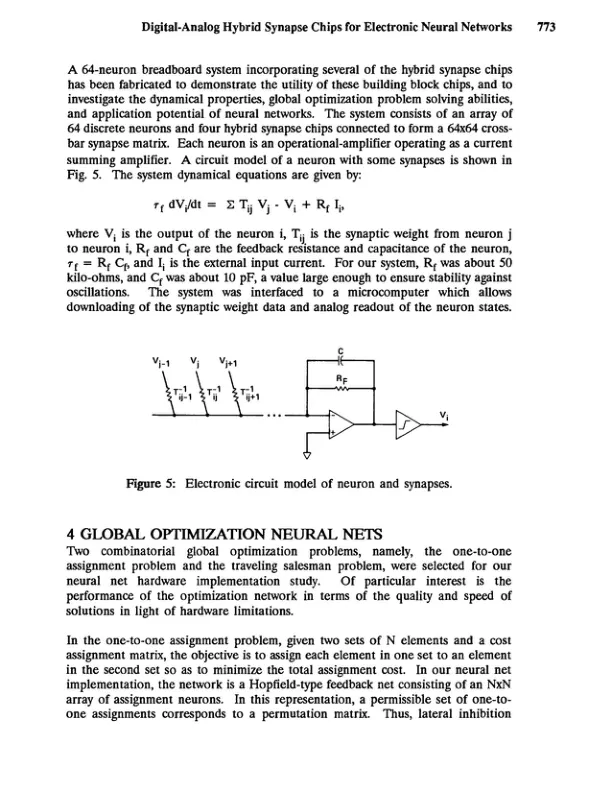

级联的 CMOS 突触芯片包含一个 32x32 (1024) 个可编程突触的交叉阵列,已被制造为用于完全并行实现神经网络的“构建块”。突触基于混合数模设计,该设计利用片上 7 位数据锁存器来存储量化权重,并利用两象限乘法 DAC 来计算加权输出。突触具有 6 位分辨率,传输特性具有出色的单调性和一致性。已制造了一个包含四个突触芯片的 64 神经元硬件,用于研究反馈网络在优化问题解决中的性能。在本研究中,已在硬件中实现了 7x7 一对一分配网络和 Hop field-Tank 8 城市旅行商问题网络。已证明该网络能够实时获得最佳或接近最佳的解决方案。

用于电子神经网络的数模混合突触芯片

主要关键词