机构名称:

¥ 1.0

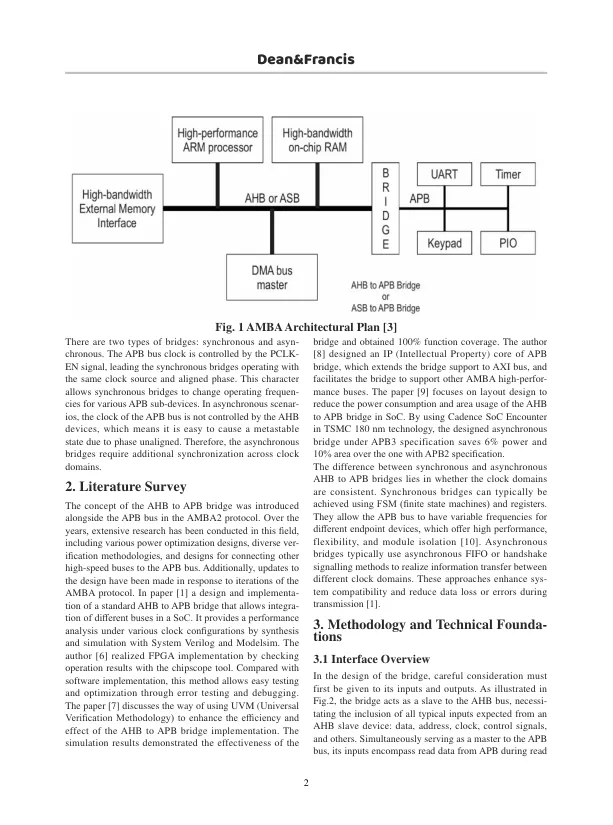

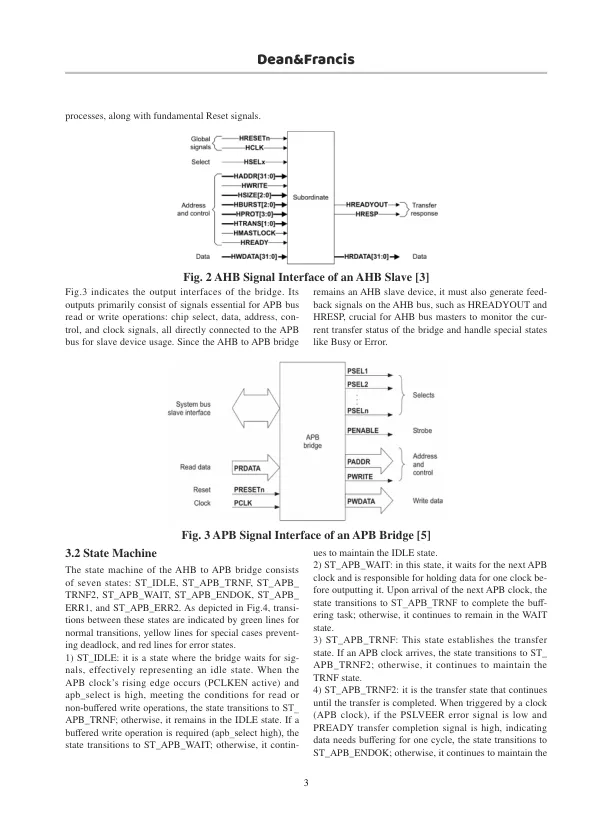

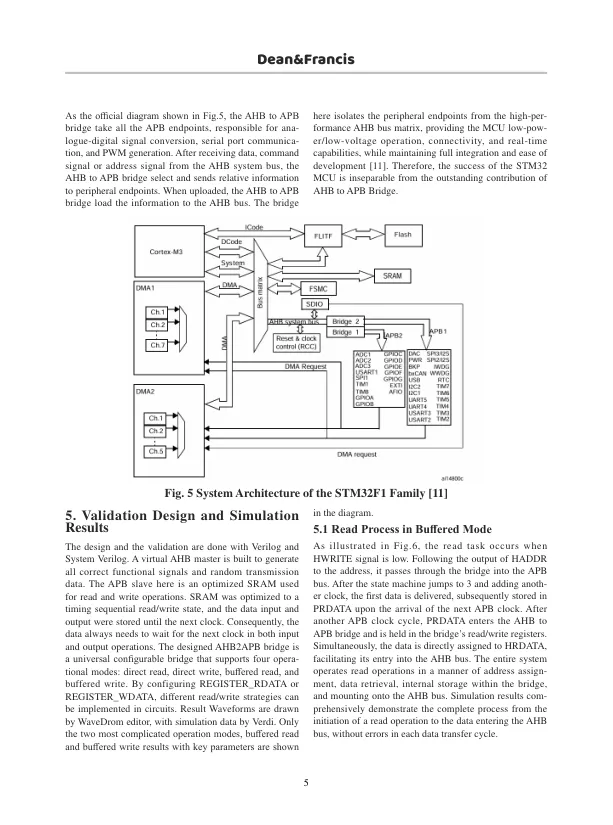

对集成系统中关键单元进行有效组合的需求日益增加。SoC 系统的开发旨在提供芯片级集成,这成为集成电路发展的必然趋势,并广泛应用于智能手机、工业应用和微控制器。ARM AMBA 协议是系统各个部分之间交互的普遍采用的方式。在 AMBA 架构中,AHB 到 APB 桥接器对于在 SoC 系统中结合高性能 AHB 总线和低功耗 APB 总线做出了重要贡献。本项目旨在使用 Verilog 实现 AHB 到 APB 桥接器,从而实现这两条总线之间的稳定数据传输。所提出的 AHB 到 APB 桥接器旨在适应不同的读写策略并确保 APB 总线上外设的正常工作。该桥接器已通过 Verilog 硬件描述语言 (HDL) 实现。创建了一个测试台,其中有一个虚拟 AHB 主机和一个优化的 SRAM 作为高速 APB 外设。Verdi 仿真表明该桥接器完全符合设计意图。关键词:AHB 到 APB 桥接器;片上系统 (SoC); AMBA 协议。

同步 AHB 至 APB 桥接的设计与实现

主要关键词