机构名称:

¥ 1.0

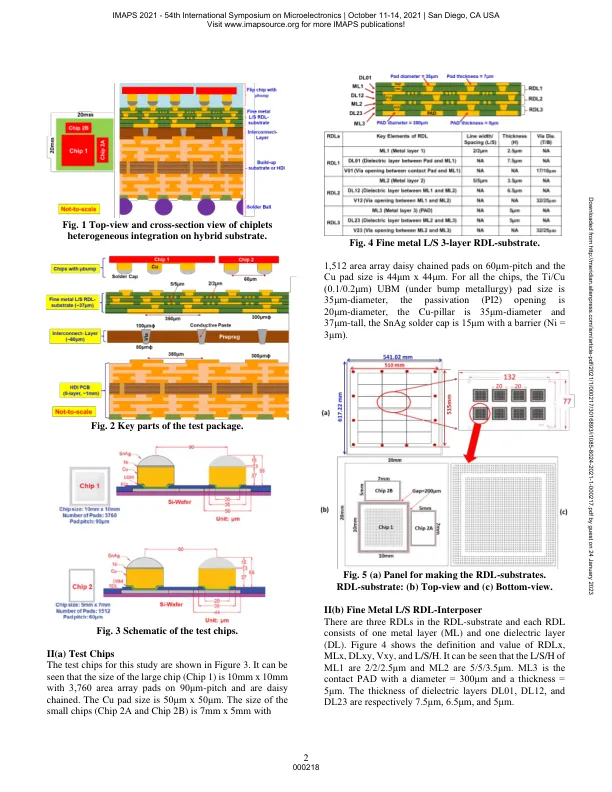

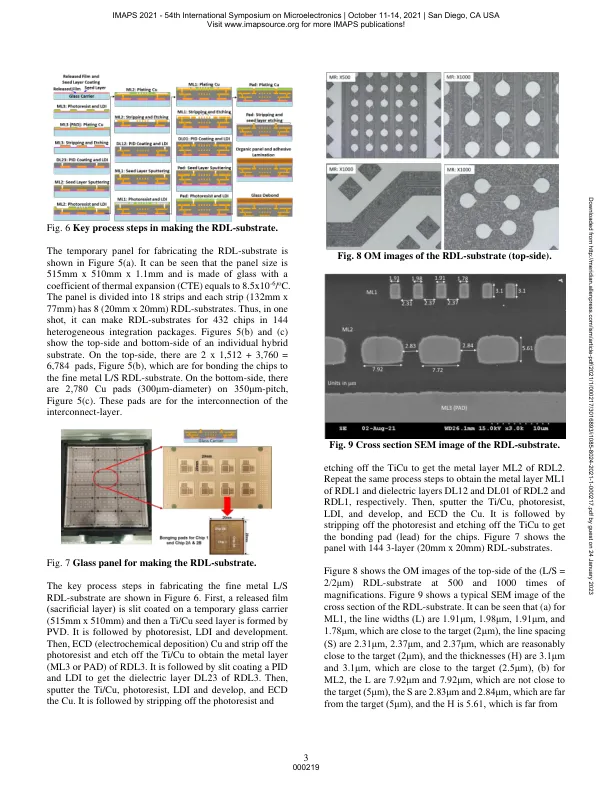

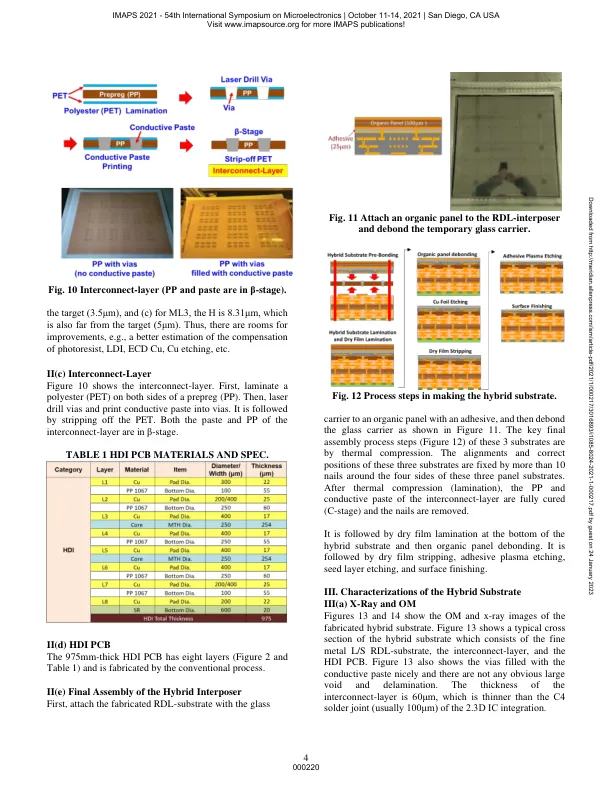

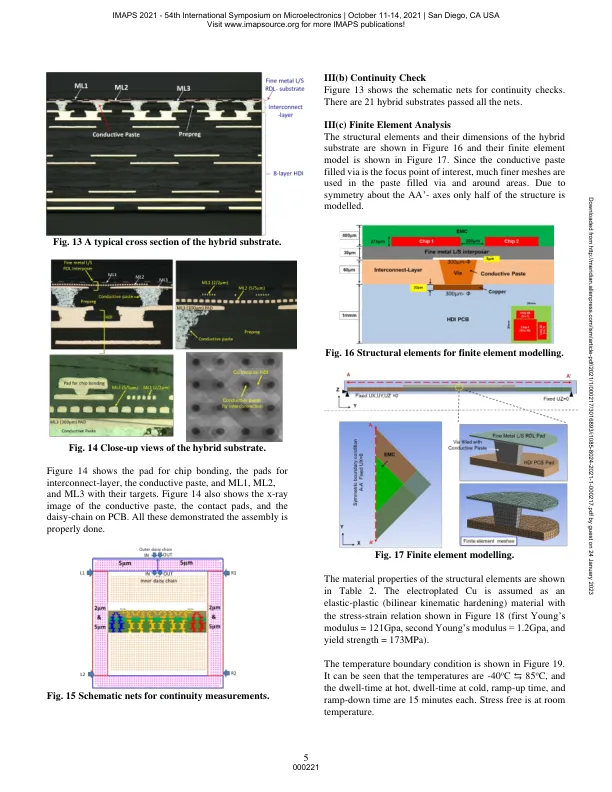

摘要在这项研究中,研究了用于chiplets的高密度有机杂交底物异质整合。重点放在与互连层的杂种底物的设计,材料,过程,制造和表征上。进行了非线性有限元分析,以显示填充有互连层导电糊的VIA处的应力状态。关键词chiplets,异源整合,杂交底物,互连层,扇出面板级芯片last I.对2.1D IC积分的简介,具有细金属线宽度(L)和间距(S)的薄膜层(无芯底物)在堆积包装基板的顶层上制造,并成为混合基板[1-5]。在这种情况下,杂交底物的屈服损失,尤其是精细的金属L/S无烷基底物很难控制,并且可能非常大。为2.3D IC积分,精细的金属L/S底物(或插头)和堆积包底物是分别制造的[6-15]。之后,细金属L/S底物和堆积封装基板通过焊接接头互连为混合基板,并通过底漆增强。在这种情况下,杂交底物的屈服损失,尤其是精细的金属L/S无烷基底物更易于控制和较小。在这项研究中,精细的金属L/S底物和堆积封装基板或高密度互连(HDI)也被单独制造,然后通过互连层组合。这与2.3d IC集成非常相似,除了焊接接头和底部填充,被取消,这些焊接被互连层取代。互连层约为60μm,由填充有导电糊的预处理和VIA(底部为100μm直径为100μm,直径为80μm),并且处于β级。精细的金属L/S无烷基基材(37μm厚度)是由PID(可令人刺激的介电),LDI(激光直接成像)和PVD(物理蒸气沉积),Photoresist和LDI,LDI,LDI,

chiplet使用互连层与高密度混合底物的异质整合

主要关键词