机构名称:

¥ 1.0

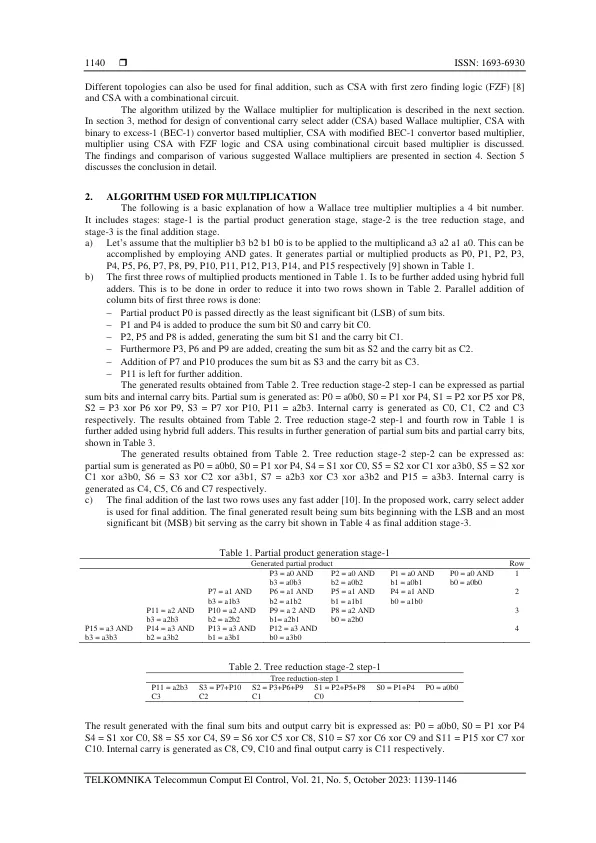

许多系统,包括数字信号处理器,有限脉冲响应(FIR)过滤器,特定于应用程序的集成电路和微处理器,请使用乘数。在当前技术趋势中,对低功率乘数的需求每天逐渐上升。在这项研究中,我们基于携带选择加法器(CSA)的4×4华莱士乘数,该乘法器使用的功率较少,并且比现有乘数具有更好的功率延迟产品。HSPICE工具用于模拟结果。与传统的基于CSA的乘数相比,功耗为1.7 µW,功率延迟产品(PDP)为57.3 fj,结果表明,Wallace Multipleer设计采用了CSA,其CSA具有首先零查找逻辑(FZF)逻辑的CSA,其功率最低1.4 µW和PDP的功率最低。

Telkomnika电信计算电子和控制

主要关键词