机构名称:

¥ 1.0

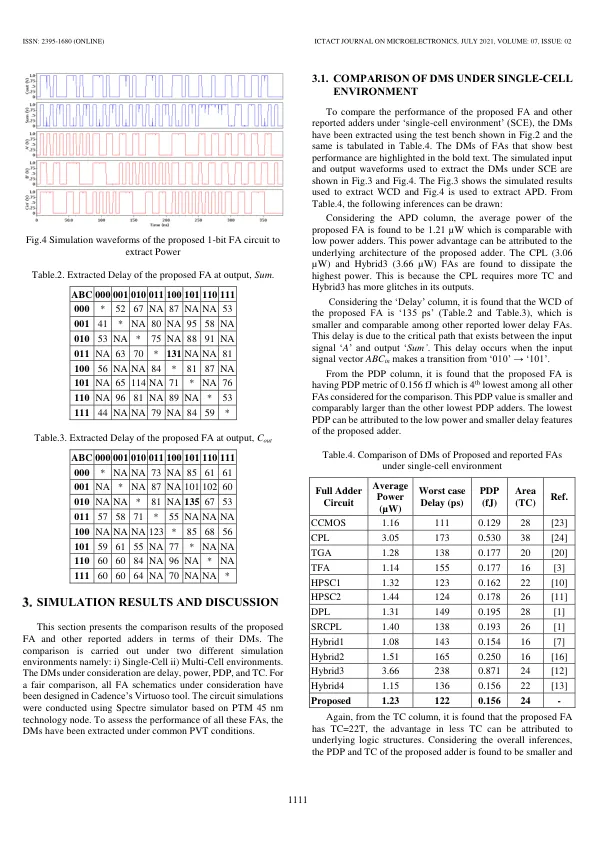

摘要 本研究论文介绍了一种用于“超大规模集成”(VLSI)应用的新型 22 晶体管 (22T)、1 位“全加器”(FA)。所提出的 FA 源自混合逻辑,该逻辑是“栅极扩散输入”(GDI)技术、“传输门”(TG)和“静态 CMOS”(SCMOS)逻辑的组合。为了评估所提出的 FA 的性能,在“设计指标”(DM)方面将其与最先进的 FA 进行了比较,例如功率、延迟、“功率延迟乘积”(PDP)和“晶体管数量”(TC)。为了进行公平比较,所有考虑的 FA 都是在常见的“工艺电压温度”(PVT)条件下设计和模拟的。模拟是使用 Cadences 的 Spectre 模拟器使用 45 nm“预测技术模型”(PTM)进行的。仿真表明,在输入信号频率 fin=200 MHz 和电源电压 V dd =1 V 时,所提出的 FA 的“平均功率耗散”(APD) 为 1.21 µW。它的“最坏情况延迟”(WCD) 为 135 ps,并且“功率延迟积”(PDP) =0.163 fJ。进一步为了评估所提出的 FA 在 V dd 和输入信号操作数大小方面的可扩展性,它嵌入在 64 位 (64b)“行波进位加法器”(RCA) 链中,并通过将 V dd 从 1.2 V 以 0.2 V 的步长降低到 0.4 V 来进行仿真。仿真结果表明,只有所提出的 FA 和其他 2 个报道的 FA 能够在不同的 V dd 值下在 64b RCA 中运行,而无需使用任何中间缓冲器。此外,我们观察到,与其他 2 个 FA 相比,所提出的 FA 具有更好的功率、延迟和 TC。关键词:全加器、PDP、低功耗、静态 CMOS、门扩散输入、传输门逻辑

用于 VLSI 的稳健且可扩展的混合 1 位全加器电路

主要关键词