机构名称:

¥ 1.0

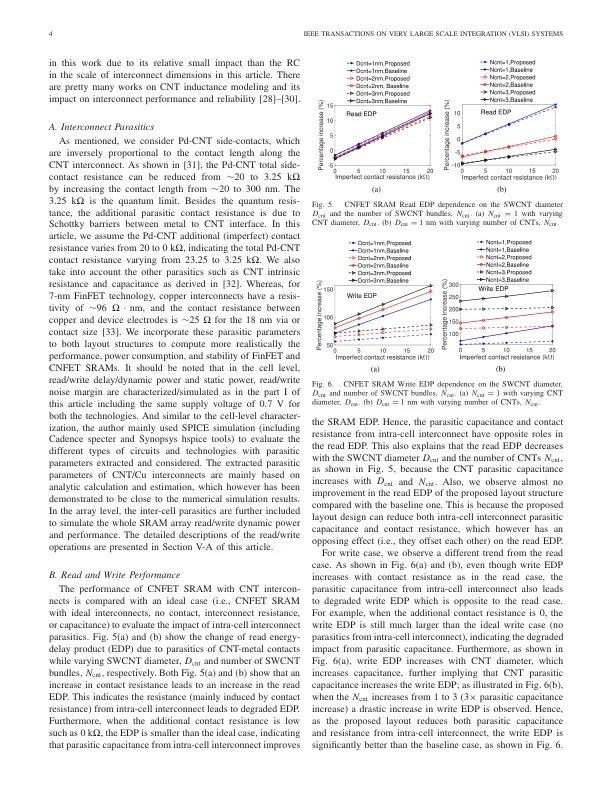

摘要 — 本文第一部分介绍了 5 纳米碳纳米管场效应晶体管 (CNFET) 静态随机存取存储器 (SRAM) 单元的尺寸和参数优化。在此基础上,我们提出了一种由原理图优化的 CNFET SRAM 和 CNT 互连组成的碳纳米管 (CNT) SRAM 阵列。我们考虑由金属单壁 CNT (M-SWCNT) 束组成的 CNFET SRAM 单元内部的互连来表示金属层 0 和 1 (M0 和 M1)。我们研究了考虑 CNFET 器件、M-SWCNT 互连和金属电极钯与 CNT (Pd-CNT) 触点的 CNFET SRAM 单元的布局结构。探索了两种版本的单元布局设计,并在性能、稳定性和功率效率方面进行了比较。此外,我们实现了一个 16 Kbit SRAM 阵列,由提出的 CNFET SRAM 单元、多壁 CNT (MWCNT) 单元间互连和 Pd-CNT 触点组成。这种阵列表现出明显的优势,其读写总能量延迟积(EDP)、静态功耗和核心面积分别为采用铜互连的7nm FinFET-SRAM阵列的0.28×、0.52×和0.76×,而读写静态噪声裕度分别比FinFET高6%和12%。

CNT 互连优化 - Enlighten Publications

主要关键词