机构名称:

¥ 1.0

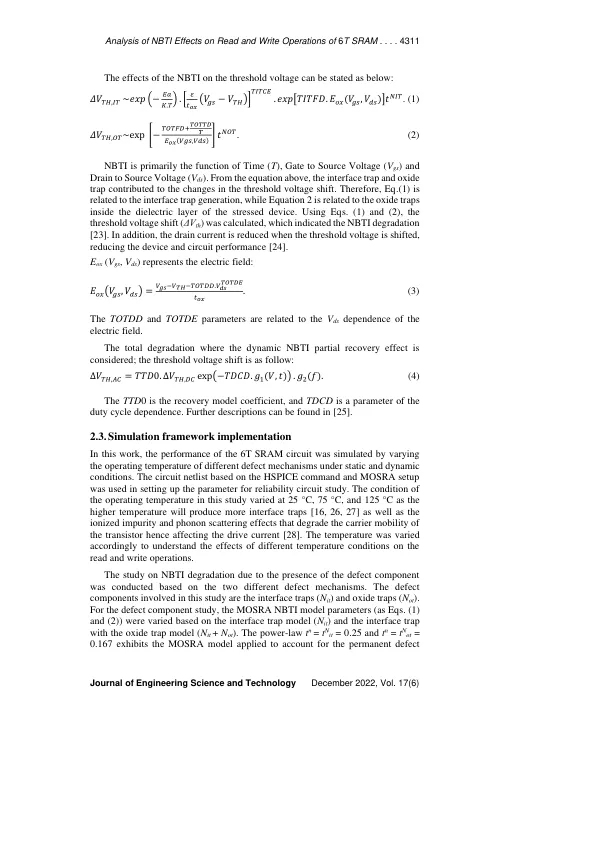

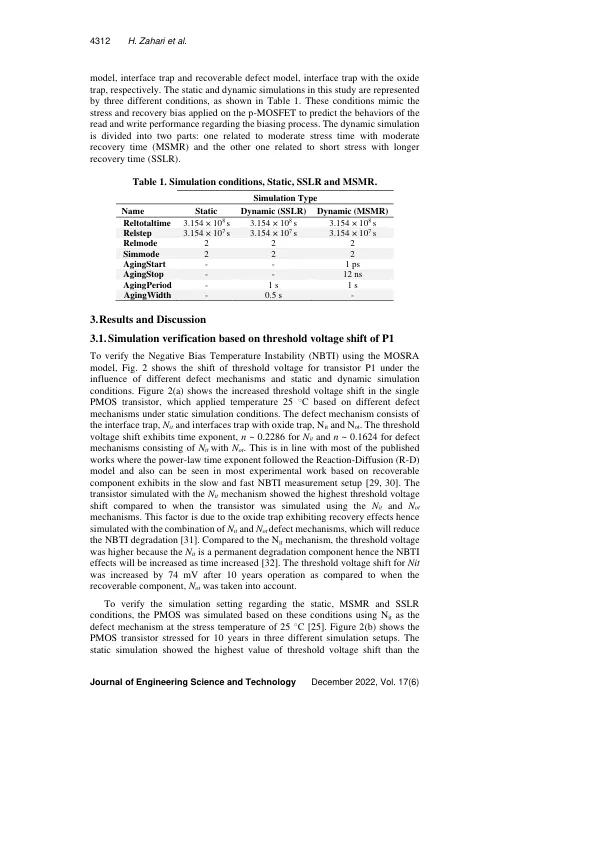

负偏压温度不稳定性 (NBTI) 是 CMOS 器件中的一个重要可靠性问题,它会影响基于 CMOS 的电路的性能。因此,了解不同缺陷机制和关于应力和恢复时间的广泛操作条件对电路性能的影响对于产生可靠且可接受的设计裕度至关重要。在这项工作中,分析了使用 16 nm FinFET 技术设计的 6T SRAM 单元电路上的 NBTI 效应。研究了 NBTI 可靠性问题对传输延迟和功耗在读写操作中的影响。研究了基于不同缺陷机制、应力时间和工作温度条件的 6T SRAM 性能。使用由 N it 和 N it 与 N ot 结合引起的缺陷计算出的阈值电压偏移之间约有 74 mV 的差异。发现读取延迟不受应力时间的影响,而写入延迟在 10 年的应力时间内略有改善。使用 N it 模拟的 6T SRAM 单元的写入延迟在运行 10 年后比使用 N it 与 N ot 组合进行模拟时提高了 0.4%。在 125°C 下,运行 10 年后读取操作的功耗高于写入操作,分别为 4.09 µW 和 0.443 µW`。观察到 6T SRAM 单元的性能取决于缺陷机制的类别、静态和动态模拟条件以及工作温度。

NBTI 对 6T 读写操作影响的分析...

主要关键词