机构名称:

¥ 1.0

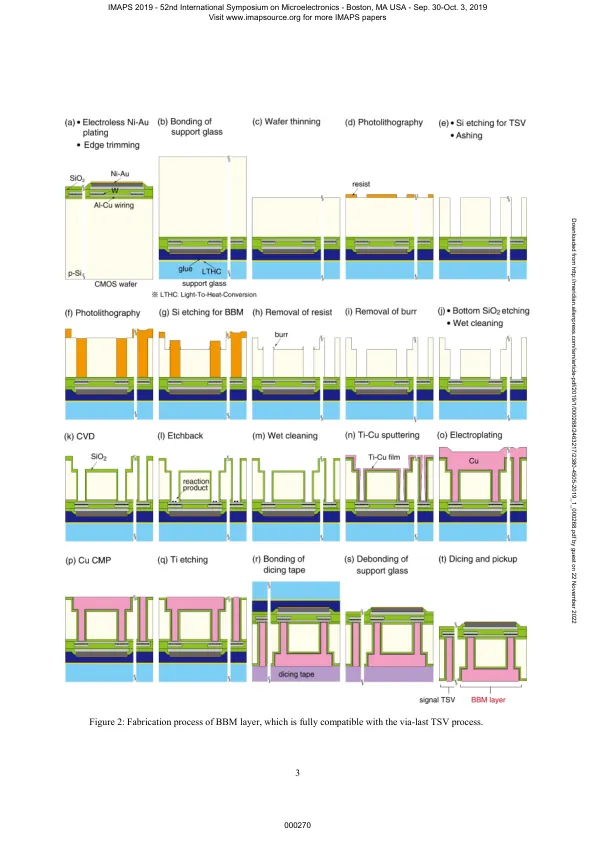

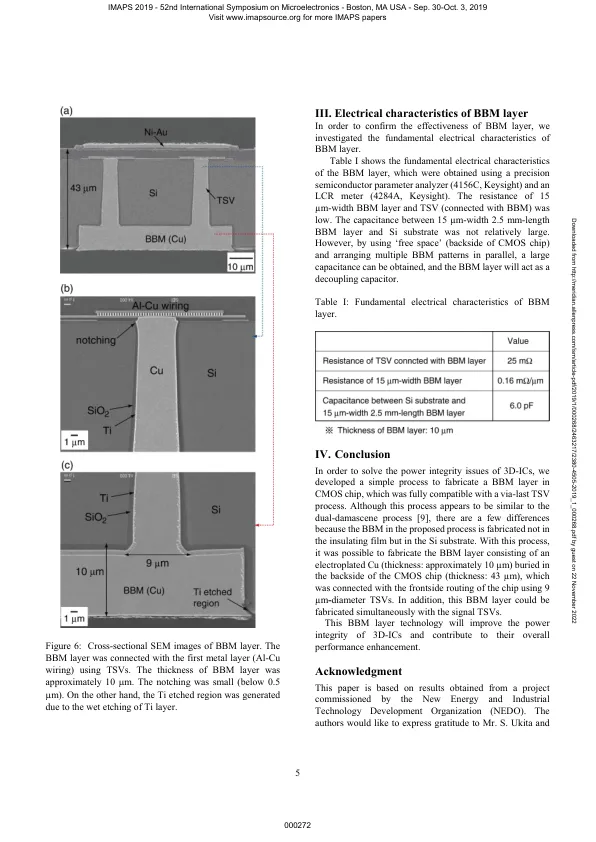

摘要 本研究开发了用于三维集成电路 (3D-IC) 的背面埋入金属 (BBM) 层技术。该技术在每个芯片背面的大片空白区域引入用于全局电源布线的 BBM 层,并与芯片正面布线并联。电源 (V DD ) 和地 (V SS ) 线的电阻因此而降低。此外,由于 BBM 结构埋入 Si 衬底中并具有金属-绝缘体-硅结构,因此可充当去耦电容。因此,引入 BBM 层可以降低电源传输网络的阻抗。3D-IC 的 BBM 层制造工艺简单,并且与后通孔硅通孔 (TSV) 工艺兼容。利用该工艺可以在 CMOS 芯片(厚度:43 µm)背面埋入由电镀 Cu(厚度:约 10 µm)组成的 BBM 层,并通过直径 9 µm 的 TSV 将 BBM 与芯片正面布线相连。 关键词 三维集成电路(3D-IC),背面埋入金属(BBM)层,硅通孔(TSV),供电网络 I. 引言 采用硅通孔(TSV)的三维集成电路(3D-IC)技术[1]–[5]是生产先进、高速、紧凑和高功能电子系统的有效方法。然而,堆叠多个芯片会导致电路设计的电源完整性问题。例如,由于可用于电源和地线的 TSV 数量有限,3D-IC 中的 IR 压降会增加。此外,在 3D-IC 中同时切换堆叠芯片时,会产生很大的同时切换噪声(di/dt 噪声)。这种同步开关噪声会在电源输送网络 (PDN) 中产生不可预测的电压变化,从而导致系统故障。为了解决这一电源完整性问题,不仅必须在电路板/中介层级降低 PDN 的阻抗,还必须在芯片级降低 PDN 的阻抗,并提高电源输送的可靠性。先前的研究提出了一些降低芯片级 PDN 阻抗的方法。第一种方法是加宽电源线/地线。这种方法非常简单,但由于线路资源有限,难以应用。

背面埋入金属层技术的发展...

主要关键词