机构名称:

¥ 1.0

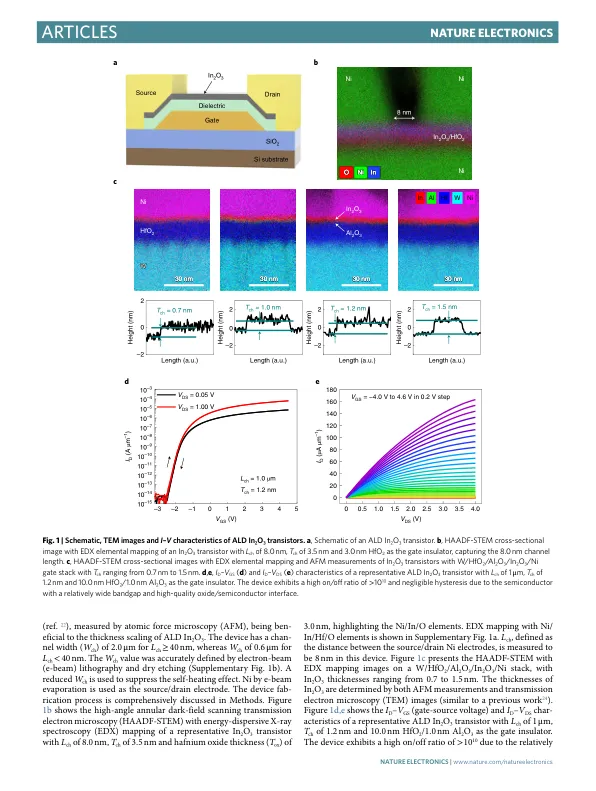

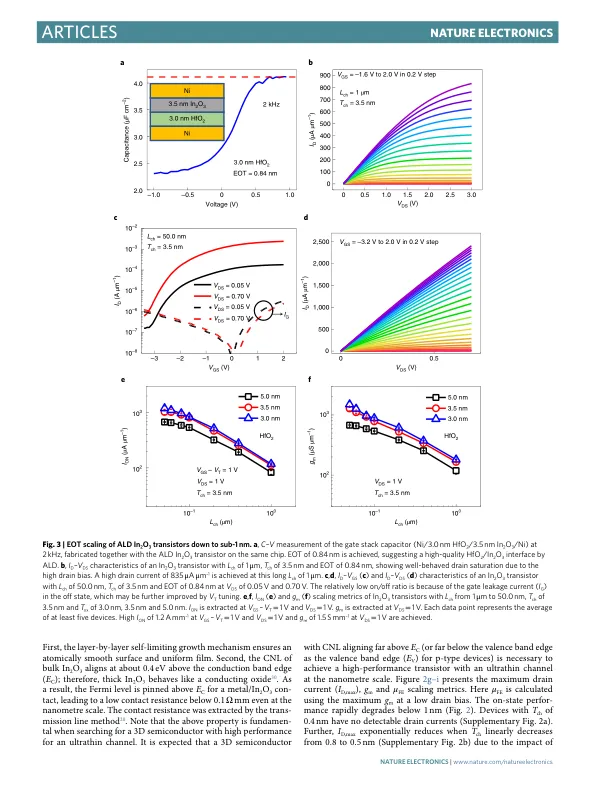

在过去的几十年中,互补的金属 - 氧化物 - 氧化 - 氧化核(CMOS)技术一直是现代综合电路发展的推动力。增强栅极静电控制以提高对短通道效应(SCE)的免疫力(尤其是在积极缩放晶体管技术的发展中)的关键策略。这包括开发高等效氧化物厚度(EOT)缩放的高κ /金属门技术,以及超薄体,鳍和堆叠的纳米片通道晶体管;在3 nm技术节点1之外,半导体工业(遵循FIN场效应晶体管技术)目前正在采用堆叠的纳米表晶体管。要进一步扩展长度尺寸并保持良好的驱动电流,至关重要的是抑制SCE。可以使用增加数量的薄堆积通道来实现这一目标。然而,常规半导体晶体管的性能迅速降低到硅的3 nm厚度低于3 nm的厚度,而INGAAS的性能降低了10 nm。二维(2D)半导体是一种替代通道材料,与传统的半导管相比,单层厚度和单层厚度较高,在单层厚度上具有更高的迁移率。但是,2D材料缺乏高品质的大区域CMOS兼容生长技术。也很难在其范德华表面形成介电。此外,这些材料很难浓缩,并且在Schottky金属/半导体触点处引起的高接触分析。特别是原子层氧化物半导体,尤其是无定形im-gallium-Zinc氧化物(Igzo) - 用于平面晶体管(TFTS)中的半导体通道材料(用于平面式式施用应用程序12)。但是,尽管是高批量制造的成熟技术,但氧化物半导体很少被视为用于缩放高性能晶体管的Channel材料。这是由于它们的低电荷载流子迁移率约为10 cm 2 v -1 s –1,并且在质量生产中使用时,它们通常需要多达几十纳米的通道厚度13。然而,对于单一三维(3D)整合应用14-21的CMOS后端(BEOL)中氧化物半导体晶体管的使用引起了兴趣。

使用原子层沉积制造的氧化二晶型晶体管

主要关键词