机构名称:

¥ 1.0

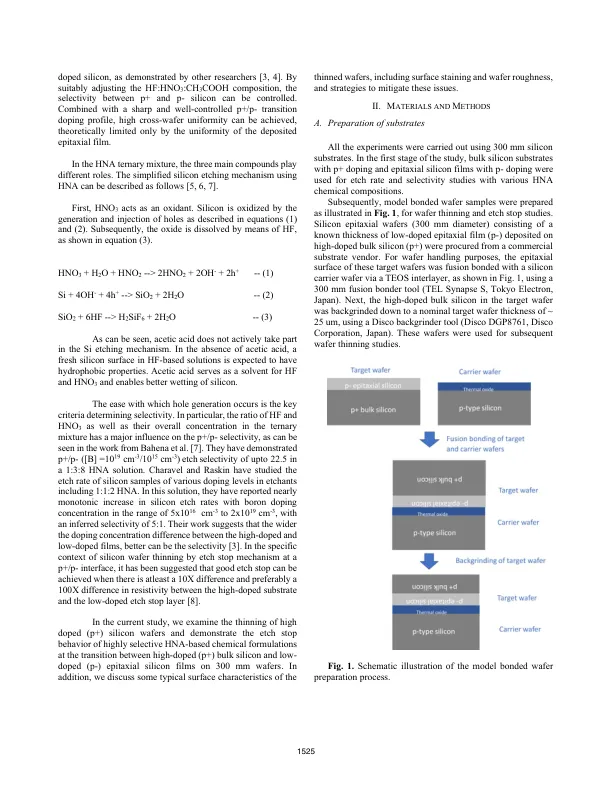

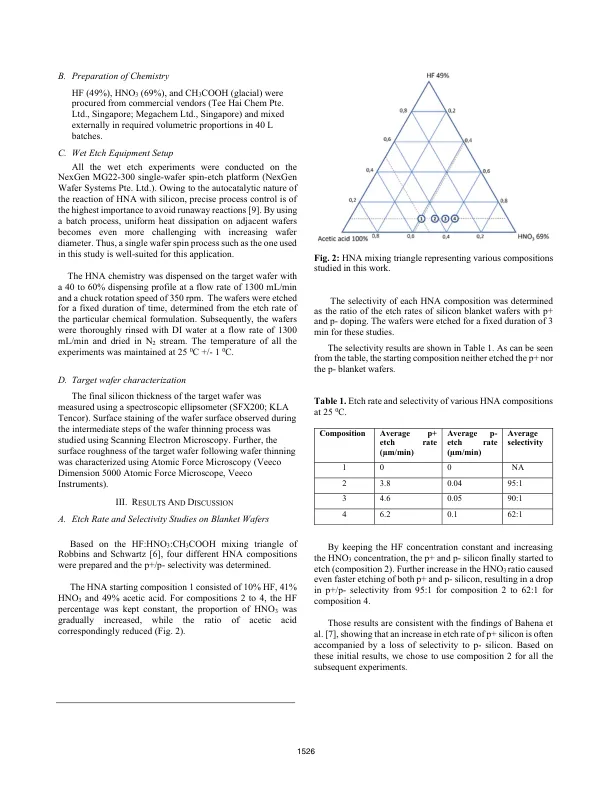

摘要 - 背面照明(BSI)3D堆叠的CMOS图像传感器对于包括光检测和范围(LIDAR)在内的各种应用中引起了重大兴趣。这些设备的3D集成中的重要挑战之一涉及单个光子雪崩二极管(SPAD)晶圆的良好控制的背面稀疏,后者堆叠着CMOS WAFERS。背面晶圆稀疏通常是通过硅的回培养和掺杂敏感的湿化学蚀刻的组合来完成的。在这项研究中,我们开发了一种基于量身定制的HF:HNO 3:CH 3 COOH(HNA)化学的湿蚀刻过程,能够在P+/P硅过渡层中实现蚀刻层,具有高掺杂级别的选择性(> 90:1)。在300毫米晶片中证明了〜300 nm的极佳总厚度变化的可行性。此外,还表征了包括染色和表面粗糙度在内的HNA蚀刻硅表面的众所周知的特性。最后,提出了一种湿的化学尖端方法来减少表面粗糙度。

掺杂选择性蚀刻 - 脱毛 - 薄薄的...

主要关键词