机构名称:

¥ 4.0

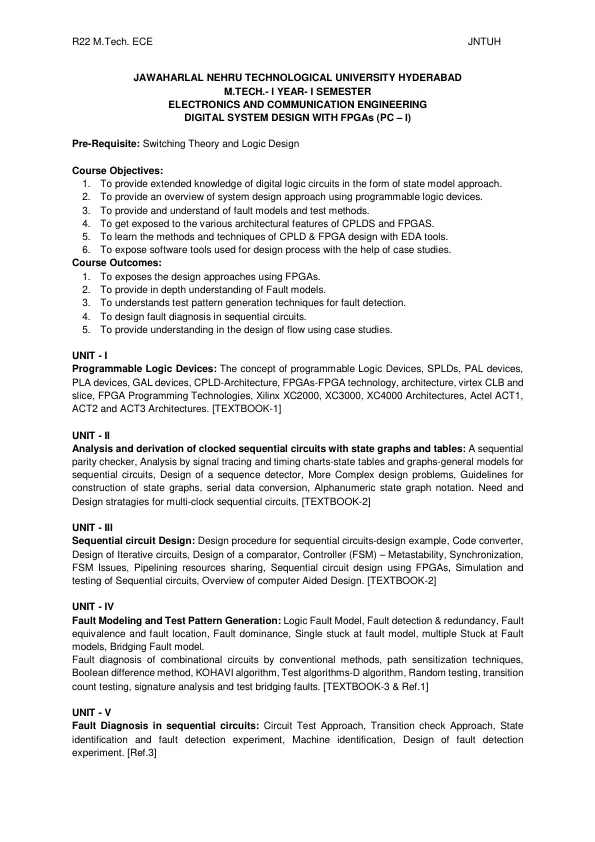

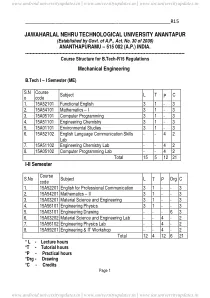

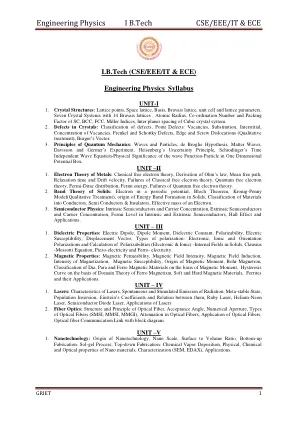

1. 揭示使用 FPGA 的设计方法。2. 深入了解故障模型。3. 了解用于故障检测的测试模式生成技术。4. 设计时序电路中的故障诊断。5. 通过案例研究了解流程设计。单元 - I 可编程逻辑器件:可编程逻辑器件的概念、SPLD、PAL 器件、PLA 器件、GAL 器件、CPLD 架构、FPGA FPGA 技术、架构、virtex CLB 和切片、FPGA 编程技术、Xilinx XC2000、XC3000、XC4000 架构、Actel ACT1、ACT2 和 ACT3 架构。 [教材-1] 第二单元 用状态图和状态表分析和推导时钟时序电路:时序奇偶校验器、信号跟踪和时序图分析-状态表和状态图-时序电路的通用模型、序列检测器的设计、更复杂的设计问题、状态图构建指南、串行数据转换、字母数字状态图符号。多时钟时序电路的需求和设计策略。[教材-2] 第三单元 时序电路设计:时序电路的设计程序-设计示例、代码转换器、迭代电路的设计、比较器的设计、控制器 (FSM) - 亚稳态、同步、FSM 问题、流水线资源共享、使用 FPGA 的时序电路设计、时序电路的仿真和测试、计算机辅助设计概述。 [教材-2] 第四单元故障建模和测试模式生成:逻辑故障模型、故障检测和冗余、故障等效性和故障定位、故障主导性、单个故障卡住模型、多个故障卡住模型、桥接故障模型。通过常规方法、路径敏感化技术、布尔差分法、KOHAVI 算法、测试算法-D 算法、随机测试、转换计数测试、签名分析和测试桥接故障对组合电路进行故障诊断。[教材-3 和参考文献 1] 第五单元时序电路中的故障诊断:电路测试方法、转换检查方法、状态识别和故障检测实验、机器识别、故障检测实验设计。[参考文献 3]

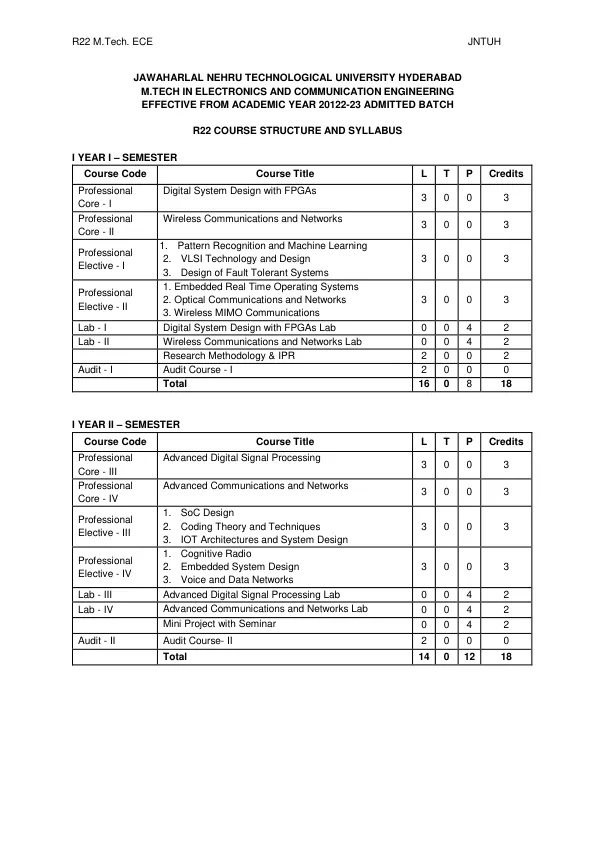

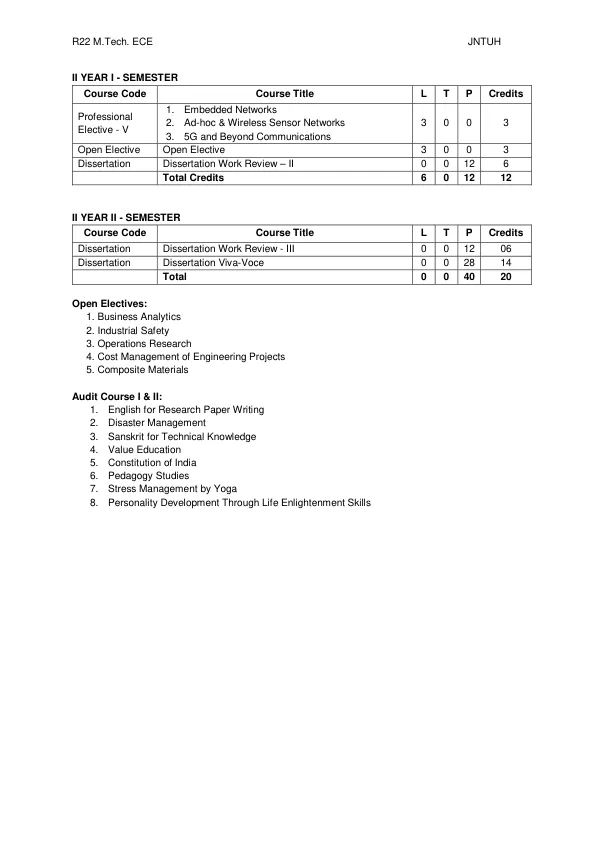

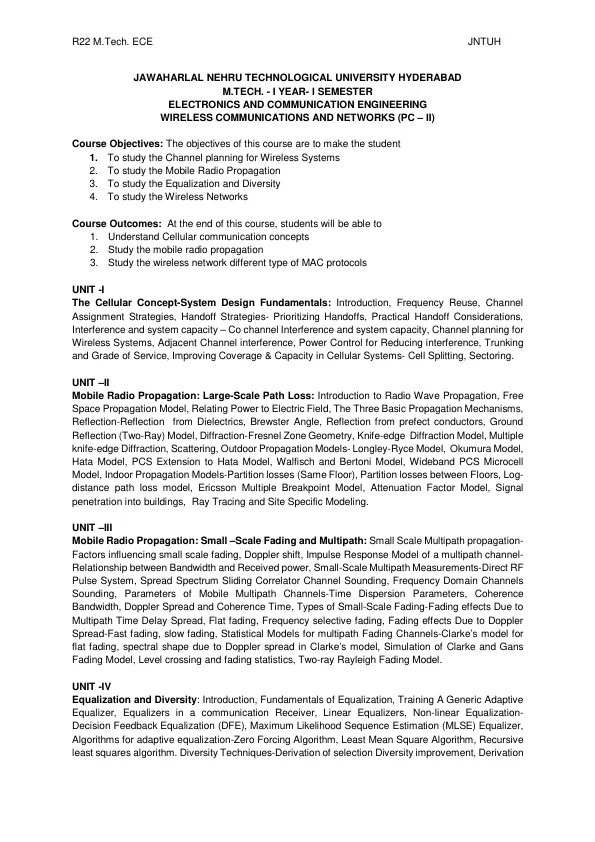

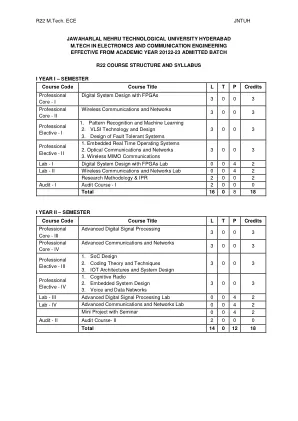

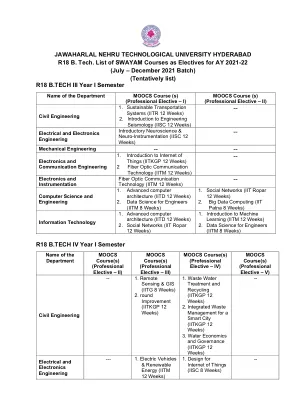

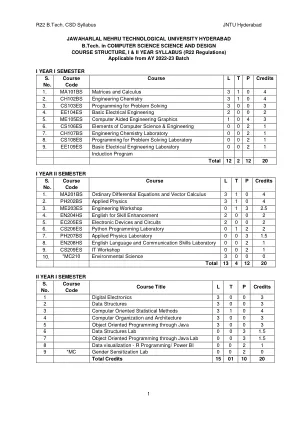

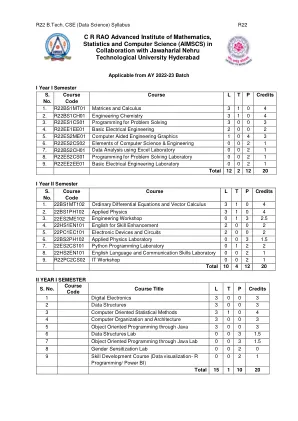

R22 M.Tech. ECE JNTUH 贾瓦哈拉尔·尼赫鲁......

主要关键词