机构名称:

¥ 1.0

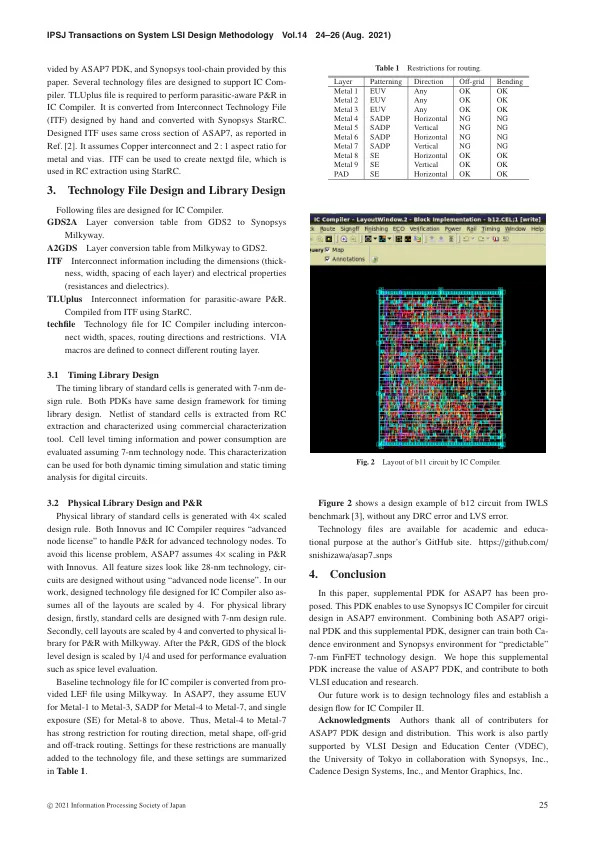

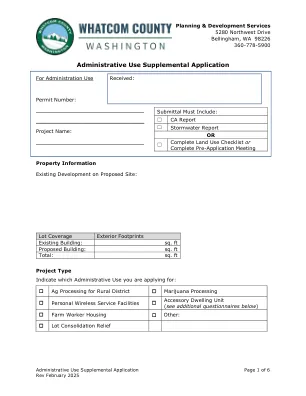

技术缩放已大大增加,并且它改善了 VLSI 芯片的功率、性能和面积。最近,7 纳米 FinFET 技术广泛用于高性能处理器和片上系统。当今的最新工艺,例如 7 纳米技术节点,使用了许多“新”技术来提高其性能和 VLSI 芯片的密度。FinFET 现在是 CMOS 晶体管的常见结构。中段线路 (MOL) 被引入以连接前端线路层和后端线路 (BEOL) 层。MOL 和 BEOL 中的局部互连层使用 EUV 光刻来提高其可布线性和密度。另一方面,半全局互连层使用 193i 自异化双重图案 (SADP) 来平衡制造成本和密度。在开始电路设计之前了解 FinFET 工艺的特点非常重要,因为它与常规平面工艺有许多不同。使用“真实”工艺设计套件 (PDK) 非常昂贵,而且很难获得访问许可。因此,“可预测”的 PDK 对于 VLSI 教育和研究都非常重要。ASAP7 是针对 7 纳米技术节点的“可预测”PDK 之一,由亚利桑那州立大学与 ARM Ltd. 合作提供 [1]。它包括定制设计流程和自动化数字设计流程,因此学习最先进的 FinFET 工艺中的这些设计流程非常有用。但是,他们仅为 Cadence Innovus 提供用于布局布线 (P&R) 的技术文件。Innovus 是一种主要的 P&R EDA,然而,Synopsys IC Compiler 也是另一个主要的 P&R 工具。本文报告了使用 IC Compiler 进行 P&R 的 ASAP7 补充 PDK。此补充 PDK 包括 Synopsys StarRC 技术文件,用于实现寄生感知 P&R。此补充 PDK 旨在添加第二种选择

使用 Synopsys Flow 的 ASAP7 补充 PDK

主要关键词