机构名称:

¥ 1.0

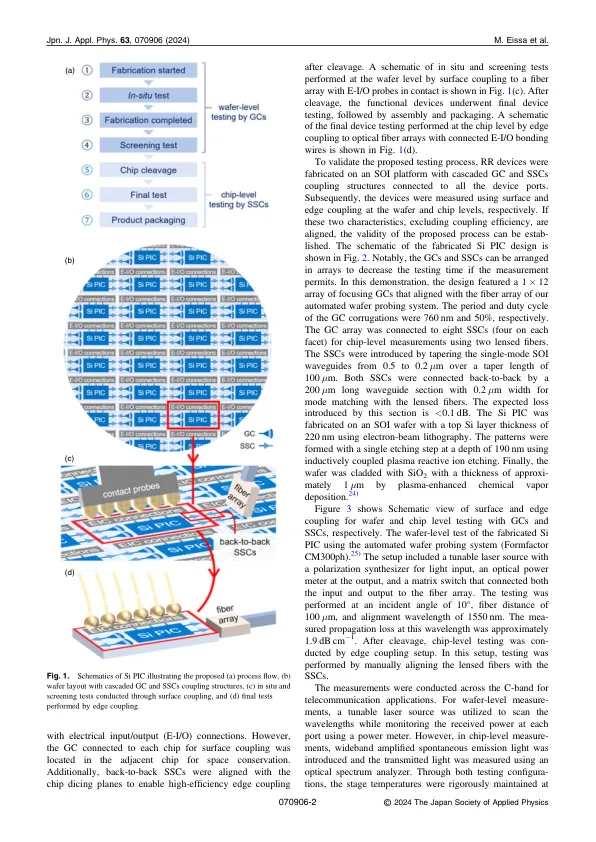

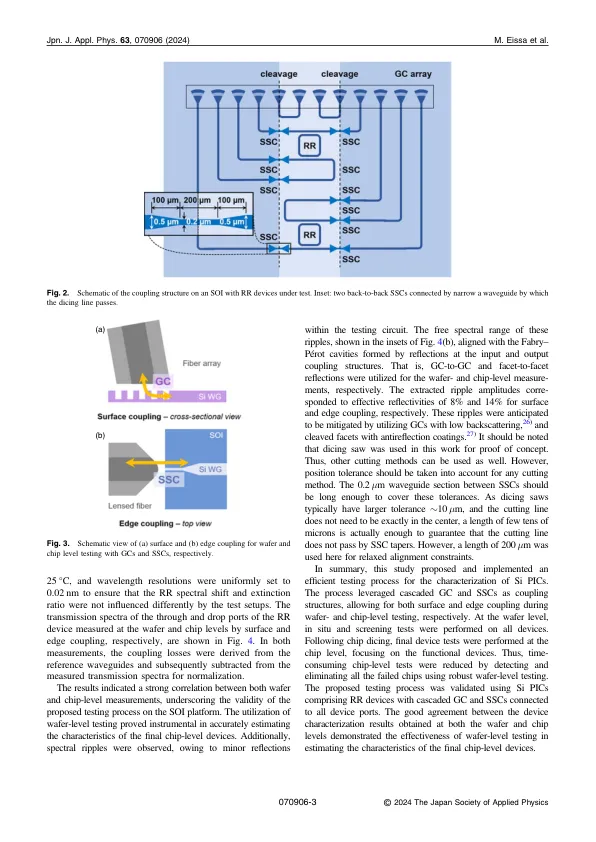

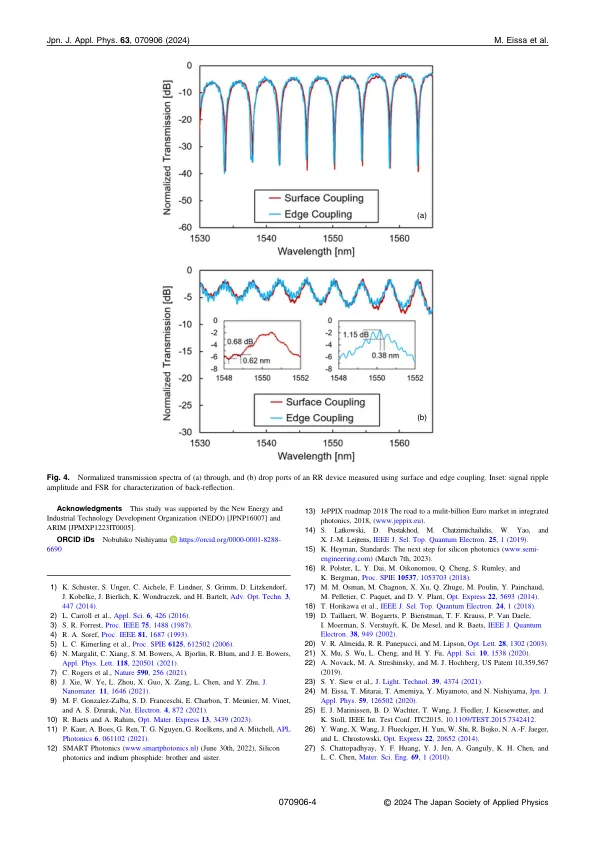

n近年来,使用CMOS兼容的过程制造硅光子IC(SI PIC)已使具有光学和电函数性具有成本效益的硅芯片的开发。1 - 5)这项技术是光子学 - 电力融合的高性能平台,可在各种行业提供有希望的应用。6 - 9)为增强硅光子学的整合和功能密度,已提出异质和杂交整合方法,以将各种材料系统与单个包装中的各种材料系统相结合。10,11)但是,基于PIC的模块的总成本受到测试,组装和包装过程的影响,这可能占常规INP PIC模块的总成本的80%。12,13)仅产品测试可贡献总成本的约29%,14)对于较不发达的硅光子技术技术,该图可能会增加到约60% - 90%。15)因此,减少测试,组装和包装成本对于降低基于SI PIC模块的整体成本至关重要。先前的研究采用了两种主要策略来降低测试成本:利用增强的测试结构,16)并增强了测试过程的自动化水平。14)在图片中,一种普遍的测试方法涉及信号通过具有不平衡分裂比的定向耦合器(例如99:1)。这种构造允许99%的信号正常通过波导,而1%的信号被击倒到测试分支。21)17)开发信号通常通过表面耦合器耦合到测试设备,从而促进了自动晶圆级测试系统用于原位和筛选测试的利用。18)然而,在组装和包装阶段,表面光栅耦合器(GCS)在带宽,极化和效率方面遇到限制。19)相比之下,利用点尺寸转换器(SSC)的边缘耦合提供了优点,例如带宽的带宽,降低极化敏感性和增强的耦合效率。20)然而,边缘耦合预先挑战,例如与SSC相关的较大足迹,固定的耦合位置,有限的对齐耐受性和耦合方面的严格规范。

边缘的晶圆和芯片级表征

主要关键词