机构名称:

¥ 1.0

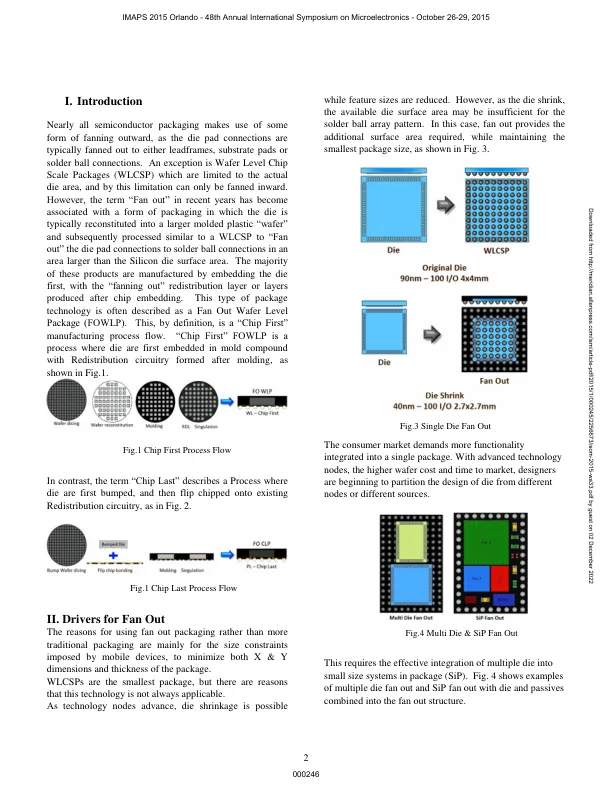

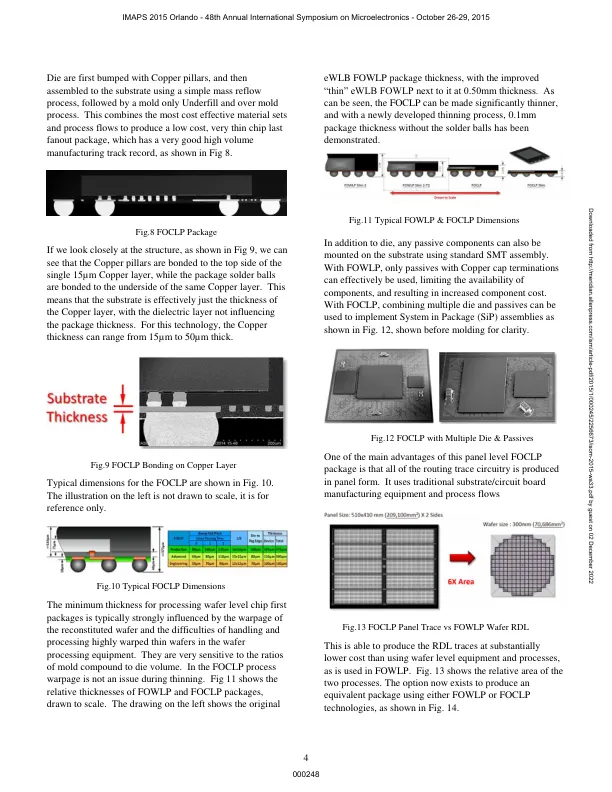

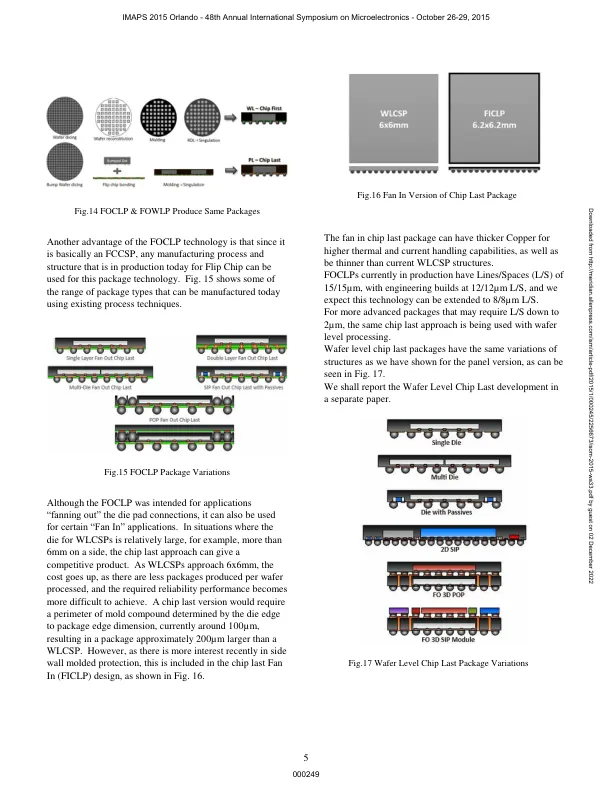

我们将介绍一种新的芯片优先 FOWLP 替代方案,该替代方案可满足大量需要 FOWLP 等封装技术的应用的需求。这种新封装已在 ASE 投入生产一年多,并使用“芯片最后”方法来解决增加可用互连焊盘面积的问题。已用铜柱 (Cu) 凸块凸起的芯片被批量回流到低成本无芯基板上,然后进行包覆成型,该包覆成型也用作芯片底部填充。Cu 柱允许以 50 µm 或更小的间距直接连接到芯片焊盘,从而无需在芯片上形成 RDL。使用嵌入式迹线允许细线和间距低至 15µm 或更小,并直接键合到裸铜上。Cu 柱键合到铜迹线的一侧,焊球或 LGA 焊盘直接位于铜的另一侧。这使得基板实际上只与走线中使用的铜一样厚,并使最终封装的厚度达到 400µm。由于这使用现有的大批量封装基础设施,因此可以轻松实现更复杂的组装,包括多个芯片、包含无源元件和 3D 结构。我们将此封装结构指定为“扇出芯片后封装 (FOCLP)”对于高端应用,我们将展示使用高密度基板工艺用于要求更高的芯片后扇出封装的能力关键词芯片先、芯片后、扇出、晶圆级封装

芯片最后扇出作为芯片优先的替代方案

主要关键词