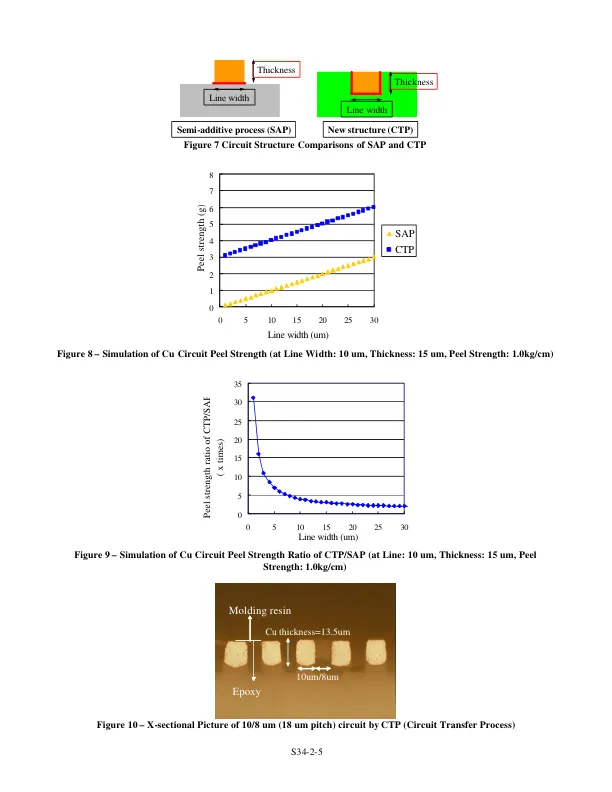

高密度PWB Ryoichi Watanabe和Hong的新电路编队技术赢得了Kim Samsung Electro-Mechanics Co.,Ltd。Suwon,S。韩国摘要为满足普华永道的未来需求,已讨论了普华永道的各种流程,材料和工具的技术。特别重要的是高端PWB的电路形成技术。在这些年中,从工业上讲,良好模式的电路形成方法已经改变了从减法过程到半添加过程(SAP)。SAP可以形成更细的电路,因为它不会引起侧面蚀刻,这是减法方法的问题。但是,SAP的闪光蚀刻过程会导致其他问题,例如由于电路之间的残留种子金属层,电路蚀刻和由于蚀刻而引起的电路分层引起的短缺陷。同样,由于形成电路的绝缘体表面的粗糙度,不仅有良好的电路形成的困难,而且是电特性的损失。在本文中,讨论了一种新的电路形成方法,以克服SAP原因闪光蚀刻过程的问题。它不需要闪光蚀刻过程,因此可以形成更细的模式。该细线电路形成的能力取决于图案抵抗分辨率,并被确认在L/S(线/空间)= 10/10UM或更少的情况下表现良好。也将电路模式埋在绝缘体层中,并且是带有绝缘体表面的刨床,因此电路具有高骨强度,具有绝缘体,并且通过制造设备或工艺之间的处理,损坏较小。此方法适用于建立PCB和FCP作为满足未来需求的电路形成技术。介绍电子设备的演变,该电子设备的发展速度更快,更小,更多功能但更具成本效益,PWBS的各种技术对于较高的密度需要各种技术。三星电力学有限公司,有限公司制造了许多PWB,例如HDI,用于手机,数字静止相机等,BGA软件包,FC BGA包装。为了满足未来的需求,特别是对于FCBGA,由于其高密度,生产FC BGA的产品变得越来越困难。电路的形成是需要在高密度方面快速进步的过程之一。已讨论了作为电路形成过程的减法过程和半添加过程(SAP),以提高其高密度。1,3但是,由于化学蚀刻而引起的减法过程具有侧面蚀刻的基本问题,并且由于闪光蚀刻过程,SAP具有局限性。SAP的闪光蚀刻过程会导致电路蚀刻等问题,如图1所示,在电路底部切割,如果闪光蚀刻不足,则在电路底部和种子层残基。由于种子层通常是铜,与电路相同,因此闪光蚀刻过程不仅蚀刻了种子层,还可以蚀刻电路。因此,电路宽度和厚度必须比闪光蚀刻之前的最终尺寸更宽,更厚,以在闪光蚀刻后保持设计规则。例如,在降低20UM电路的底部分离后,如图1所示,仅粘附的宽度仅为20UM螺距,如图1所示。这被认为是不足以为20UM电路提供足够的剥离强度。当电路变得更细时,由于制造输送机或滚筒的处理损坏,底切将是一个更大的问题,制造业产量将更低。出于这些原因,需要基于新概念的电路形成技术才能使线路电路形成并解决这些技术困难。

高密度PWB

主要关键词