机构名称:

¥ 1.0

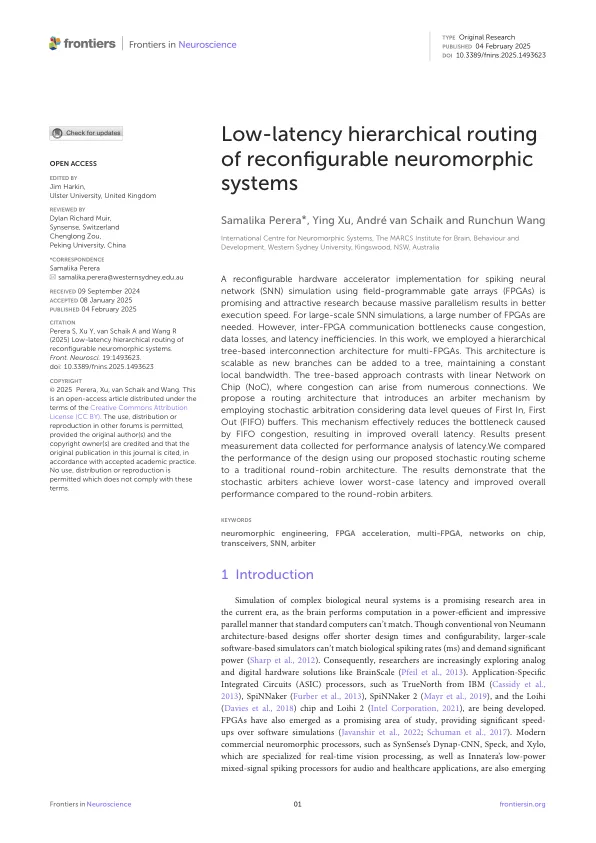

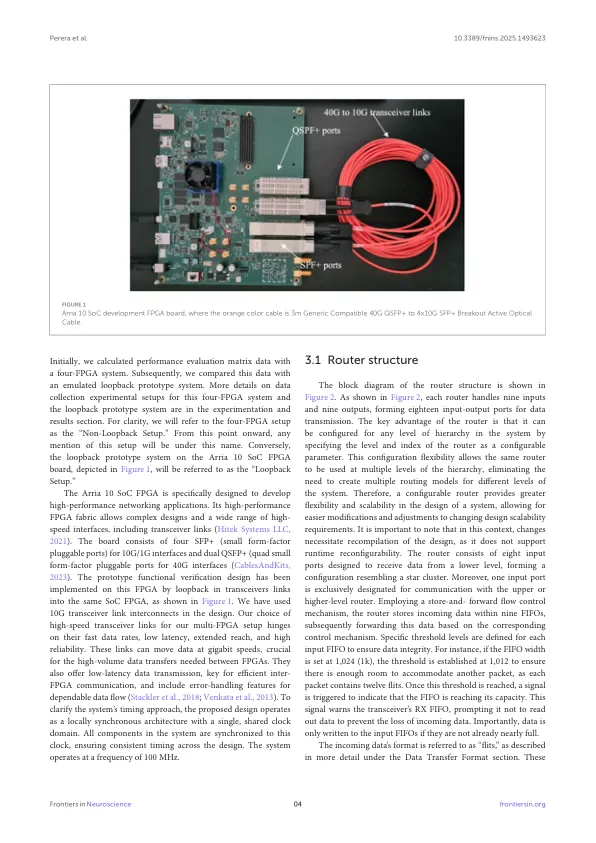

使用现场可编程门阵列 (FPGA) 实现可重构硬件加速器以进行脉冲神经网络 (SNN) 模拟是一项有前途且有吸引力的研究,因为大规模并行性可以提高执行速度。对于大规模 SNN 模拟,需要大量 FPGA。然而,FPGA 间通信瓶颈会导致拥塞、数据丢失和延迟效率低下。在这项工作中,我们为多 FPGA 采用了基于树的分层互连架构。这种架构是可扩展的,因为可以将新分支添加到树中,从而保持恒定的本地带宽。基于树的方法与线性片上网络 (NoC) 形成对比,在片上网络 (NoC) 中,拥塞可能由众多连接引起。我们提出了一种路由架构,该架构通过采用随机仲裁引入仲裁器机制,考虑先进先出 (FIFO) 缓冲区的数据级队列。该机制有效地减少了由 FIFO 拥塞引起的瓶颈,从而改善了整体延迟。结果显示了为延迟性能分析而收集的测量数据。我们将使用我们提出的随机路由方案的设计性能与传统的循环架构进行了比较。结果表明,与循环仲裁器相比,随机仲裁器实现了更低的最坏情况延迟和更高的整体性能。

可重构神经形态系统的低延迟分层路由

主要关键词